Архив новостей из мира FPGA

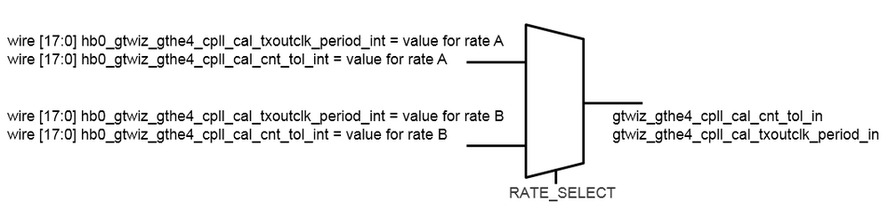

Руководство: Как динамически изменять скорость передачи данных в GTH/GTY трансиверах в ПЛИС Xilinx UltraScale/UltraScale+ В блоге компании Xilinx появилось руководство по динамическому изменению line-rate при передаче данных с помощью GTH/GTY трансиверов в ПЛИС семейств UltraScale/UltraScale+.

1758

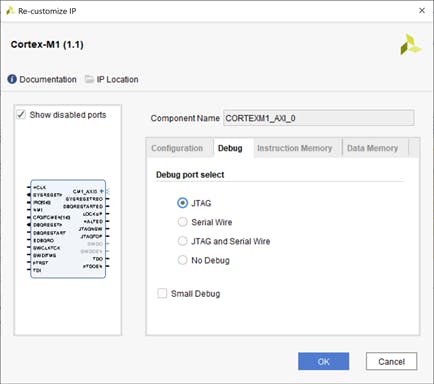

Руководство: Отладка софт-процессоров ARM Cortex-M1 и Cortex-M3 на FPGAНа портале hackster.io появилось новое руководство от Адама Тейлора, в котором он описывает процесс конфигурирования и отладки софт-процессора ARM Cortex-M1 с помощью вн ... Читать дальше »

1733

1

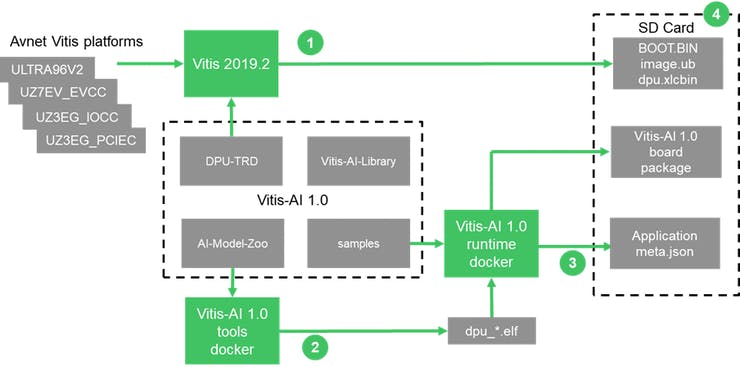

Руководство: Проектирование в Vitis AI для Ultra 96 На портале hackster.io появилось новое руководство по работе с Vitis AI. В статье в пошаговом режиме рассмотрено развертывание нейронной сети на отладочной плате Ultra 96.

1342

0

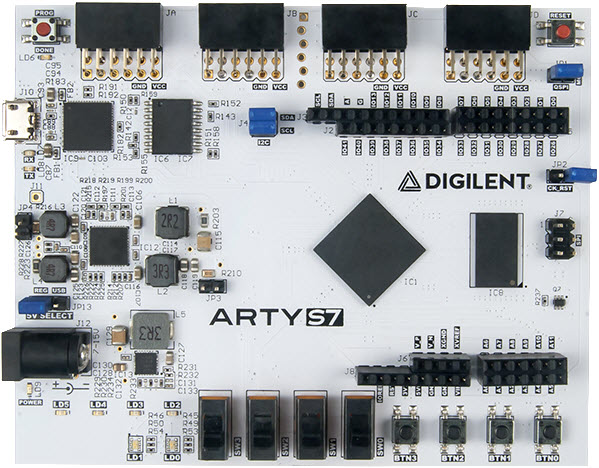

Руководство: Подборка материалов для работы с Arty-S7 (Spartan-7) С чего начать изучать ПЛИС начинающему разработчику? Ну наверное, с поиска туториалов и гайдов по данному направлению. Согласитесь, что наличие готовых материалов для быстрого старта - это одна из основных причин по которым стоит отдать предпочтение при выборе отладочной платы.

1687

0

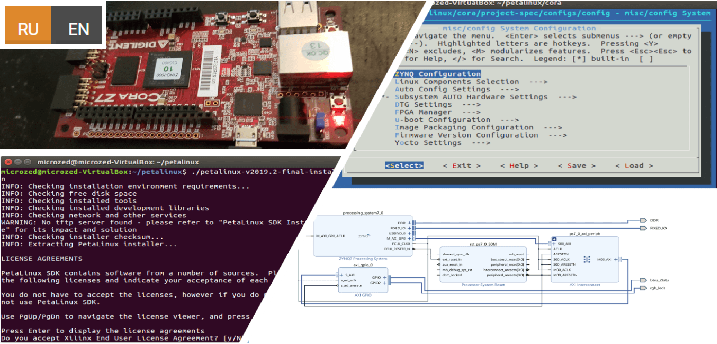

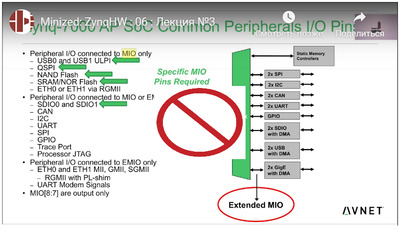

Руководство: Цикл статей по сборке PetaLinux для СнК Xilinx Zynq

В цикле статей Adam Taylor рассказывает о том, как установить PetaLinux на виртуальную машину, сконфигурировать элементы и создать встроенное решение для SoC Zynq

1. ... Читать дальше »

5307

0

Руководство: Цикл статей по работе с алгоритмами Computer Vision в Vitis для встраиваемых систем

На проекте Beetlebox, начиная с декабря 2019 с завидной регулярностью публикуются статьи/руководства по настройке и работе с алгоритмами компьютерного зрения для встраиваемых систем на основе СнК Xilinx Zynq с использованием единой программной платформы Vitis. На момент написания этой новости опубликовано 4 части, с ... Читать дальше »

1834

0

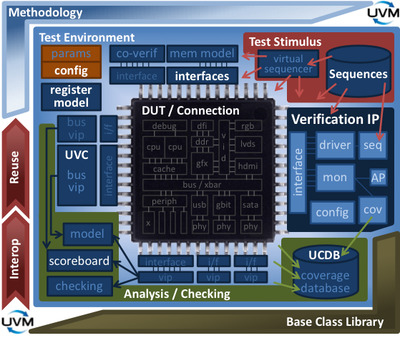

Вебинар: Руководство по программированию UVM: советы и хитрости о которых вы могли и не догадываться

Краткий обзор Ведущий вебинара, Крис Спир, представляет руководство по работе с UVM (универсальной методологии верификации). Он даст рекомендации по разработке тестовых транзакций и классов компонентов, которые будут просты в отладке и повторно применяемы. Отдельно будут рассмотрены правила ... Читать дальше »

1623

0

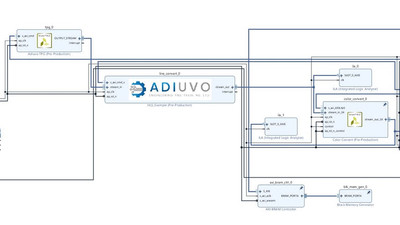

Руководство: Создание видео потоков в Vivado HLSНа портале hackster.io появилось новое руководство от Adam Taylor, в котором он описывает маршрут проектирования пользовательского IP ядра для видеообработки с помощью Viva ... Читать дальше »

1653

0

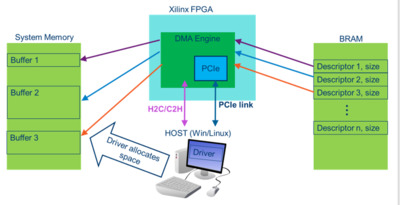

Руководство: Как реализовать DMA контроллер в ПЛИС Xilinx - часть 1 На портале LinkedIn выложен обширное руководство по реализации DMA с ядрами Xilinx.

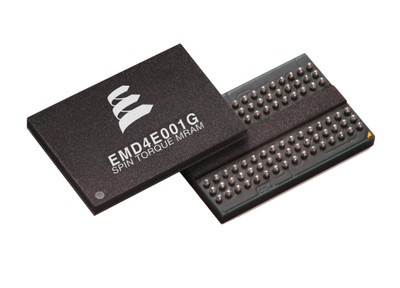

Руководство: Использование памяти Everspin 1Gb STT-MRAM с Xilinx контроллером DDR4Компания Everspin Technologies (производитель магниторезистивной памяти MRAM) анонсировала полное руководство по использованию своей памяти STT-MRAM 1 Гбит в системах х ... Читать дальше »

1583

2 |

0