Пролог: Исследование Функциональной Верификации Исследовательской Группы Уилсона 2020 Года

Это первая статья из серии блогов, в которых представлены результаты нашего нового исследования функциональной верификации Wilson Research Group 2020 года. Как и в моей предыдущей серии блогов Wilson Research Group functional verification study 2018 года, я планирую разделить обсуждение на FPGA и IC/ASIC.

Обзор исследования

Результаты исследования, представленные в этой серии статей, являются продолжением серии отраслевых исследований по функциональной верификации, которые начались в 2007 году и продолжались раз в два года, начиная с 2010 по 2020 год. Каждое из этих исследований было смоделировано по образцу исследований collett International Research, Inc. 2002 и 2004 годов и сосредоточено на рынке IC/ASIC. Когда мы начали изучать рынок ПЛИС в 2012 году, мы ждали, пока у нас появится достаточно данных для выявления тенденций верификации, чтобы сделать какие-либо существенные выводы.

Для целей нашего исследования была построена рандомизированная выборка из нескольких полученных отраслевых списков. Это позволило нам охватить все регионы мира и все соответствующие сегменты рынка электронной промышленности. Важно отметить, что мы не включили в выборку список наших клиентов. После очистки данных результатов для удаления несогласованных, неполных или случайных ответов окончательный размер выборки состоял из 1492 подходящих участников (т. е. n=1492).

доверительный интервал

Поскольку все исследования, основанные на опросах, подвержены ошибкам выборки, мы пытались количественно оценить эту ошибку в вероятностных терминах, вычисляя доверительный интервал. Для нашего исследования мы определили общую погрешность в размере ±3%, используя 95% доверительный интервал. Другими словами, этот доверительный интервал говорит нам, что если бы мы взяли повторные выборки, 95% выборок попали бы в пределы нашей погрешности ±3%, и только 5% выборок попали бы за ее пределы.

Участники исследования

В этом разделе я предоставляю справочную информацию о структуре исследования.

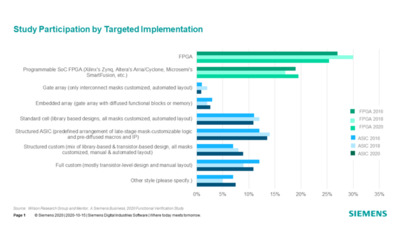

На рис. 1 сравнивается процентная доля участников исследования 2016, 2018 и 2020 годов (т. е. проектных проектов) по целевому внедрению как для проектов IC/ASIC, так и для проектов FPGA. Важно отметить, что целенаправленная реализация не представляет собой объем кремния с точки зрения мирового рынка полупроводников, поскольку на один проект может приходиться значительная часть доходов рынка полупроводников.

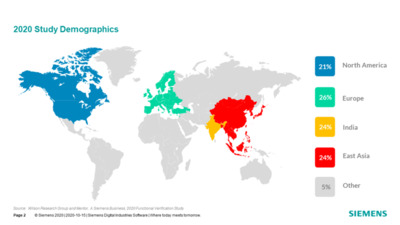

Наше исследование Wilson Research Group 2020 года является всемирным исследованием, и на рисунке 2 показана карта покрытия по различным регионам мира. Опросы проводятся как на глобальном, так и на региональном уровнях. В этом цикле статей мы представим глобальные тенденции.

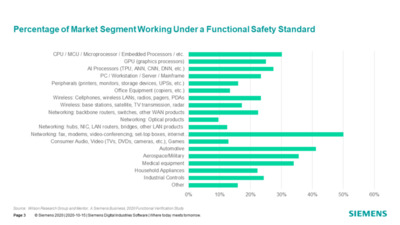

На рис. 3 показана доля участников общего исследования FPGA и IC/ASIC в разбивке по сегментам рынка. Важно отметить, что эти цифры не отражают объем кремния по сегментам рынка.

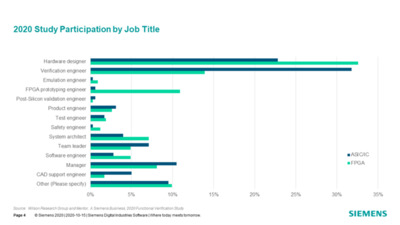

На рис. 4 показан процент общего числа участников, имеющих право на участие в исследовании FPGA и IC/ASIC, в разбивке по их должностным обязанностям. Примером подходящего участника может служить инженер по проектированию или верификации или менеджер, который активно работает в электронной промышленности. В целом, инженеры по проектированию и верификации составляли большинство участников исследования.

Прежде чем я начну представлять результаты нашего исследования функциональной верификации 2020 года, я планирую обсудить в следующей статье общие проблемы предвзятости, связанные со всеми исследованиями, основанными на опросах, и то, что мы сделали, чтобы свести эти проблемы к минимуму.

| Ссылка на оригинал | Мотивировать на продолжение |