Архив новостей из мира FPGA

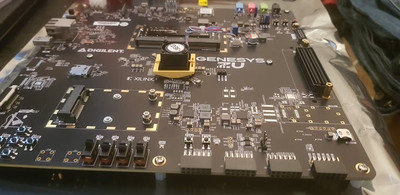

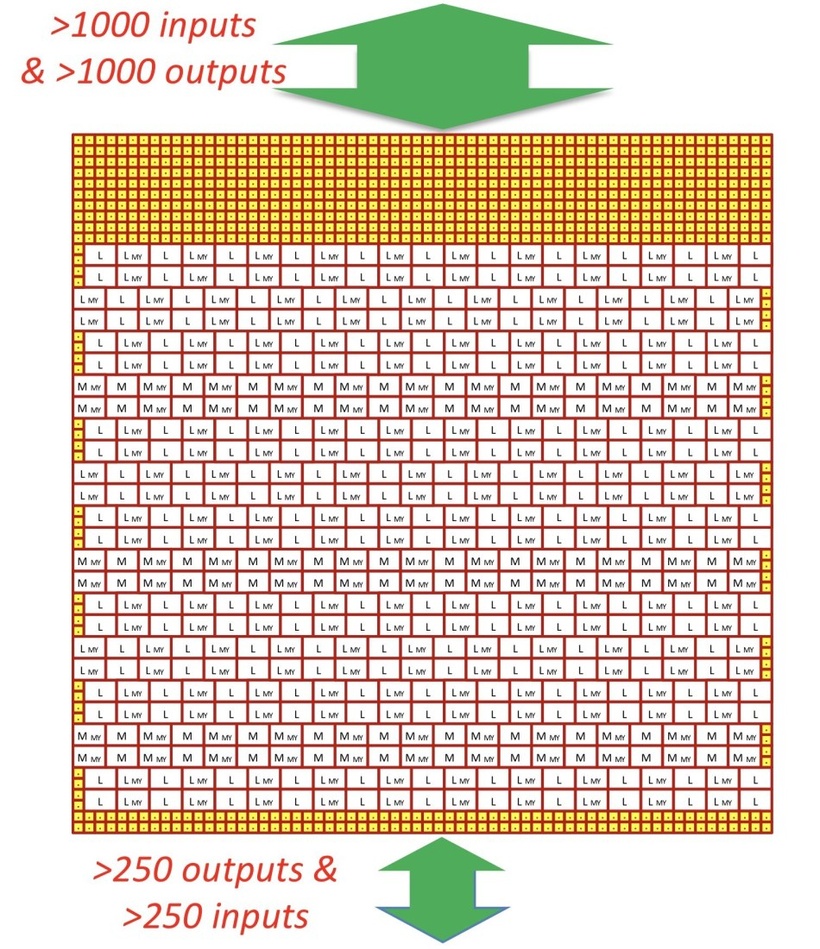

Новое руководство от Адама Тейлора: высокопроизводительная обработка изображений на Genesys ZU 3EG Реализация конвейера обработки изображений на Genesys ZU 3EG с использованием новейших IP-ядер от Xilinx.

1436

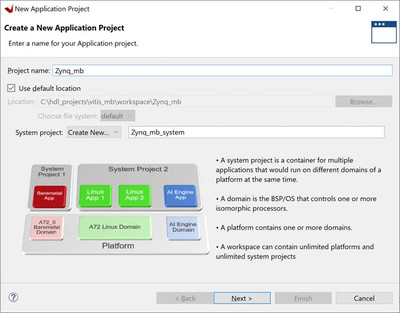

Новое руководство: Создание многопроцессорной системы в Vitis: Zynq + MicroBlaze Ранее мы рассматривали то, как мы можем использовать Vitis для встроенных систем на Zynq и Zynq MPSoC.

1863

0

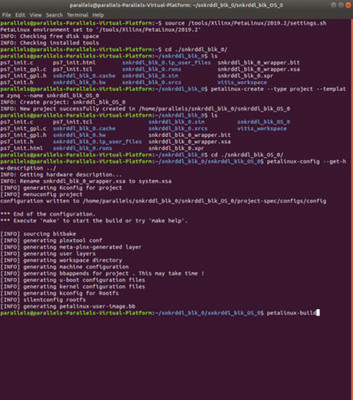

Руководство: Petalinux и Snickerdoodle BlackНа hackster.io появилось новое руководство по развертыванию Linux с помощью Petalinux для отладочного комплекта Snickerdoodle Black, ... Читать дальше »

1543

0

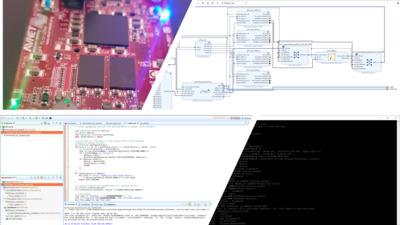

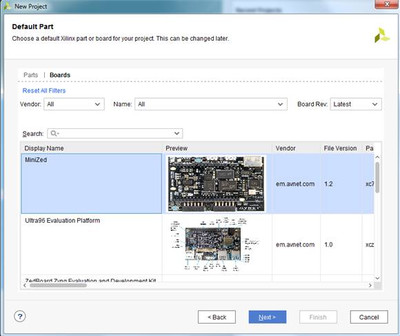

Руководство: Создание платформы для MicroZed в VITISАдам Тейлор опубликовал новое руководство по созданию описания платформы в VITIS для отладочного модуля MicroZed. В целом этот процесс моло чем отличается от предыдущих ... Читать дальше »

1512

0

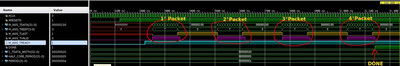

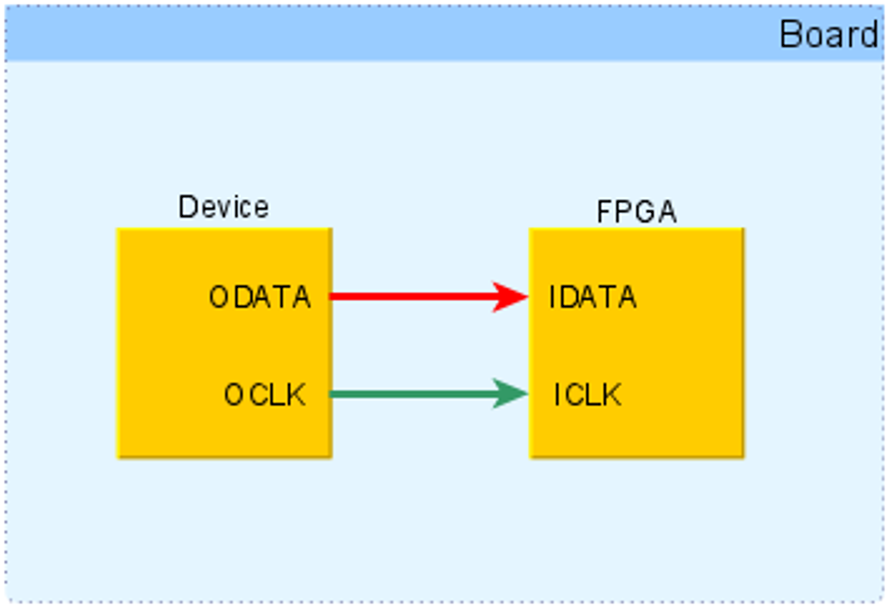

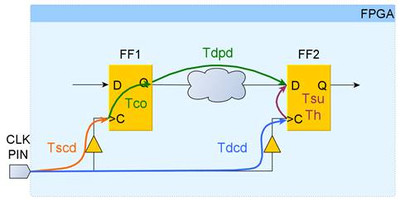

Руководство: Основы AXI - Моделирование интерфейса AXI с помощью AXI Verification IP (AXI VIP)В блоге компании Xilinx появилось новое руководство по работе с интерфейсом AXI - AXI Basics 2 - Simulating AXI interfaces with the AXI Verif ... Читать дальше »

2261

0

Новое руководство: Скрипт Net2axisПри разработке устройств на FPGA часто возникает необходимость симуляции сетевого трафика. Избавиться от столь рутинной процедуры вам поможет скрипт Net2axis. Новый видео руководство: Интерфейсы :: MIPI :: Часть 1 :: Тестовый проект для SP701На YouTube канале нашего проекта опубликовано новое видео руководство по сборке тестового проекта с использованием MIPI интерфейса и отладочного комплекта SP701.

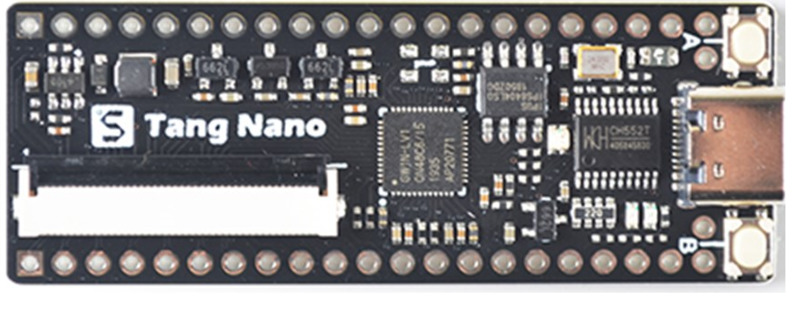

Новое руководство: Китай, GOWIN, АО "Восток", ПЛИС - лучше меньше, да лучше! Некоторое время назад мы писали о такой китайской компании GoWin, которая производит бюджетные ПЛИС и так же упоминали о небольшом отладочном комплекте на их основе.

1867

0

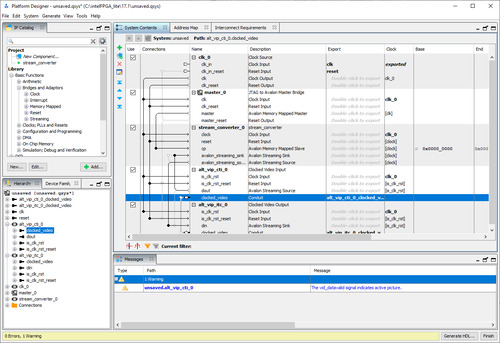

Новое руководство: Создание пользовательского IP-ядра в Qsys/Platform DesignerВ статье рассмотрен способ создания пользовательских IP-ядер в Intel Qsys/Intel Platform Designer. И Intel Qsys, и Intel Platform Designer являются компонентами среды Intel Quartus. Разница между Qsys и Platform Designer невелика: во втором незначительно расширен функционал. Qsys используется в более старых версиях Qua ... Читать дальше »

1754

0

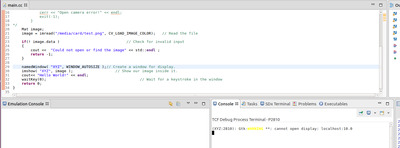

Новое руководство: Визуальная отладка OpenCV приложений для Zynq US+ в Xilinx SDK При разработке и отладке приложений OpenCV применяется так называемый визуальный дебагигнг. Т.е. в произвольных местах программы удобно выводить на экран изображение, с которым работаете для отладки алгоритма. В этой статье я хотел бы поделиться опытом по работе в Xilinx SDK с приложением OpenCV. |

0