Профилирование примера выполнения нейросети из репозитория Vitis-AI на ZCU104

В состав Vitis-AI (#vitisai) входит программа для профилирования "vaitrace". В видео https://youtu.be/vGu4aaXh6KA показаны необходимые действия для запуска примера с профилированием. Используется Vitis 2020.2 и #ZCU104.

Предполагается что уже выполнены следующие этапы:

- Собран проект FPGA с кернелом DPU

- Записана SD

- ZCU104 запущена.

- Установлен пакет vitis-ai-runtime-1.3.0 .tar.gz

- Установлен архив vitis_ai_runtime_r1.3.0_image_video.tar.gz

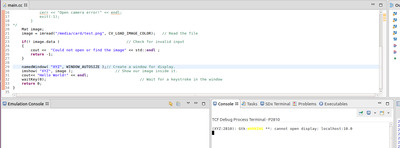

На самом видео показаны следующие действия:

- Соединение с платой ZCU104 и запуск примера без профилирования

- Запуск примера с профилированием

- Скачивание результатов профилирования на компьютер

- Анализ результатов в программе vitis_analyser

В комментарии есть подробный timeline.

P.S. видео без звука.