Краткая сводка научных статей, с упоминанием FPGA/ПЛИС (Март 2024 / часть 1)

Предлагаем читателям небьольшую подборку зарубежных начно-технических статей с упоминанием ПЛИС

- Реализация гибридного метода маркировки пятен волнового фронта по методу Шака-Гартмана на ПЛИС

В данной работе представлена реализация в реальном времени гибридного метода маркировки связанных компонентов для обработки изображений датчика волнового фронта Шака-Гартмана в системе адаптивной оптики (АО). Выходное изображение датчика волнового фронта представляет собой изображение пятен. Во время работы датчика может случиться так, что сильно искаженные волновые фронты (ВФ) могут привести к смещению пятен за пределы их субапертуры, что может привести к снижению производительности системы АО.

В этой статье рассказывается о преимуществах высокопроизводительных вычислений и параллельной обработки на программируемой логической интегральной схеме (FPGA). Задача состоит в том, чтобы вычислить центроиды этих пятен. Для достижения этой цели был исследован гибридный метод маркировки. Сначала этот метод был реализован с использованием прямого и обратного сканирования с соответствующей маской для каждого сканирования. Кроме того, после маркировки каждой линии применяется процесс перемаркировки, который выполняется в обоих направлениях. После маркировки для вычисления центроидов было параллельно реализовано несколько блоков обработки. Каждый блок отвечает за вычисление центроида одной метки. Система работает в реальном времени с задержкой в один кадр, то есть выходное изображение представляет собой слияние текущего кадра и центроидов предыдущего кадра.Прямая и обратная маркировка требует большого объема памяти, поэтому в данном исследовании мы ограничились только прямой маркировкой. Прямая маркировка была успешно реализована, и центроиды были обнаружены в условиях минимальных точечных искажений. Эта реализация прямой маркировки также работает в реальном времени со значительным сокращением задержки при вычислении центроидов, что приводит к минимизации общей задержки системы AO, позволяя ускорить вычисления и коррекцию, а также сократить использование памяти до 1 % по сравнению с использованием прямой и обратной маркировки на 81 %, что является преимуществом аппаратной реализации.

PDF -

Использование битово-последовательных архитектур для аппаратно-ориентированных ускорителей глубокого обучения с потоком данных с буферизацией столбцов

Полученные результаты подтверждают, что наша разработка исключительно подходит для приложений, требующих компактных, маломощных и работающих в режиме реального времени решений.

Битовые последовательные ускорители нейронных сетей удовлетворяют растущую потребность в компактных и энергоэффективных инструментах глубокого обучения. Традиционные нейросетевые ускорители, несмотря на свою эффективность, часто сталкиваются с проблемами размера, энергопотребления и универсальности при решении различных вычислительных задач.

Для решения этих проблем в данной статье представлен подход, основанный на интеграции битовой последовательной обработки данных с передовыми методами обработки потока данных и архитектурными оптимизациями. Центральным элементом этого подхода является поток данных с буферизацией столбцов (column-buffering - CB), который значительно снижает требования к доступу и перемещению входной карты признаков (input feature map - IFM), тем самым повышая эффективность. Более того, упрощенный процесс квантования эффективно устраняет смещения, оптимизируя общий процесс вычислений. Кроме того, в данной работе представлен тщательно разработанный ускоритель LeNet-5, использующий архитектуру массива элементов обработки конволюционного слоя (onvolutional layer processing element array - CL PEA), включающую улучшенный блок последовательного умножения-накопления (multiply–accumulate unit - MAC).

Эмпирически наша работа демонстрирует лучшие показатели по частоте, площади кристалла и энергопотреблению по сравнению с современными ASIC. В частности, наша разработка использует меньше аппаратных ресурсов для реализации полного ускорителя, достигая высокой производительности 7,87 GOPS на Xilinx Kintex-7 FPGA с коротким временем обработки 284,13 мкс.

PDF -

Расширение беспроводной сети с низкой задержкой для промышленного Интернета вещей

Своевременная доставка критически важных сообщений в условиях реального времени является растущим требованием для промышленных сетей Интернета вещей ( industrial Internet of Things - IIoT). Подобно проводным технологиям сетей с чувствительностью ко времени (time-sensitive networking - TSN), которые раздваивают потоки трафика на основе приоритета, предлагаемый беспроводной метод направлен на обеспечение быстрой доставки критически важного трафика через несколько переходов для реализации многочисленных вариантов использования IIoT.

Архитектуры IIoT переходят к беспроводным соединениям, что создает желание расширить функциональность TSN до беспроводного формата. Существующие протоколы обладают неотъемлемыми проблемами для достижения этой приоритетной связи с низкой задержкой, начиная от жестко запланированных передач с временным разделением, масштабируемости/дрожания протоколов множественного доступа с учетом несущей (carrier-sense multiple access - CSMA) и заканчивая задержками, вызванными шифрованием. В данной статье представлена аппаратно подтвержденная технология низких задержек, основанная на методах множественного доступа с кодовым разделением по назначению приемника (receiver-assigned code division multiple access - RA-CDMA), для реализации безопасного беспроводного расширения, подобного TSN, подходящего для IIoT.

Результаты работы нашего аппаратного прототипа, созданного на платформе IntelFPGA Arria 10, показывают, что (суб-)миллисекундные задержки при передаче по одному каналу могут быть достигнуты для каждого из доступных типов сообщений в диапазоне от 12 бит до 224 бит полезной нагрузки. Благодаря достижению односторонней передачи менее 1 мс, надежное беспроводное расширение TSN, сопоставимое по времени с 802.1Q и/или 5G, вполне достижимо и доказано в концепции с помощью нашего аппаратного прототипа.

PDF -

Основные подходы к снижению энергопотребления в схемах с конечными автоматами - обзор

В обзоре рассматриваются методы снижения энергопотребления в схемах конечных автоматов (finite state machines - FSM). В обзоре изложены основные подходы к решению этой проблемы, разработанные за последние 40 лет. Показаны основные источники рассеивания мощности в КМОП-схемах, проанализированы статические и динамические составляющие этого явления. Снижение энергопотребления может быть достигнуто за счет использования грубозернистых (coarse-grained) методов, общих для всех цифровых систем.

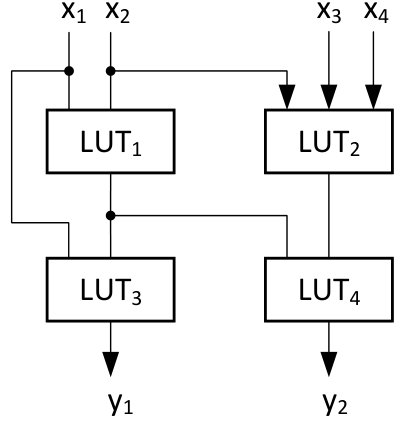

Эти методы основаны на масштабировании напряжения и/или тактовой частоты. В обзоре приведены основные структурные схемы, возникающие при использовании этих методов при оптимизации энергетических характеристик FSM-схем. Также известны различные тонкие методы, учитывающие специфику как самих FSM, так и используемых логических элементов. Анализируются три группы тонких методов, ориентированных на FSM-схемы на базе ПЛИС. К ним относятся тактовая синхронизация, назначение состояний и замена элементов таблицы поиска (look-up table - LUT) на встроенные блоки памяти (embedded memory blocks - EMB). Тактовая регулировка предполагает раздельное или совместное использование таких подходов, как (1) декомпозиция входов FSM и (2) отключение входов FSM. Целью назначения энергосберегающих состояний является снижение коммутационной активности результирующей схемы FSM. Замена LUT на EMB позволяет снизить энергопотребление за счет уменьшения количества элементов схемы FSM и их взаимосвязей.

Мы надеемся, что данный обзор поможет специалистам использовать известные и разрабатывать новые методы снижения энергопотребления. Мы считаем, что хорошее знание и понимание существующих методов снижения энергопотребления является необходимым условием для разработки новых, более эффективных методов решения этой очень важной проблемы. Хотя рассмотренные методы в основном ориентированы на FSM на базе ПЛИС, при необходимости они могут быть модифицированы и использованы для оптимизации энергопотребления схем FSM, реализованных с использованием других логических элементов.

PDF -

Алгоритм VFF-RLS на основе ПЛИС для обнаружения изоляции батареи в электромобилях

По мере распространения электромобилей (electric vehicles - EV) все большее внимание уделяется обеспечению безопасности эксплуатации EV. Экспоненциальный рост аккумуляторных технологий за последние несколько лет изменил представление о хранении энергии и вызвал революцию в нескольких отраслях. Деградация изоляции батарей при регулярном использовании вызывает серьезную озабоченность. Высокое напряжение (high voltage - HV) и уровень тока в HV электромобилях представляют собой значительную электрическую угрозу.

Развитие технологии электромобилей привело к увеличению присутствия HV электрического оборудования во всем автомобиле. Прочность изоляции и раннее обнаружение состояния здоровья батарей имеют важное значение для обеспечения безопасности в электромобилях. В данной статье рассматриваются различные методы обнаружения изоляции и разработка алгоритмов адаптивного фильтра (adaptive filter - AF) на основе FPGA для обнаружения изоляции. ПЛИС являются одними из наиболее точных и быстрых методов обнаружения среди всех методов обнаружения изоляции, используемых до сих пор в электромобилях.

В данном исследовании предлагается алгоритм VFF-RLS на базе ПЛИС для эффективной реализации обнаружения изоляции (insulation detectio) в электромобилях. Результаты экспериментальных испытаний с использованием ПЛИС показывают, что предложенный метод может быстро отслеживать изменения сопротивления изоляции (IR). Метод на основе ПЛИС VFFRLS работает достаточно хорошо, чтобы уменьшить ошибки при работе с изменениями напряжения и сопротивления на клеммах батареи.

PDF

Продолжение следует

PS: ищем авторов статей для первого отечественного FPGA журнала. Вся информация на странице издания