RAD для софт-процессоров и немного «сферических коней в вакууме»

Немного хулиганства в области софт-процессоров. Пока предварительные размышления и проба пера

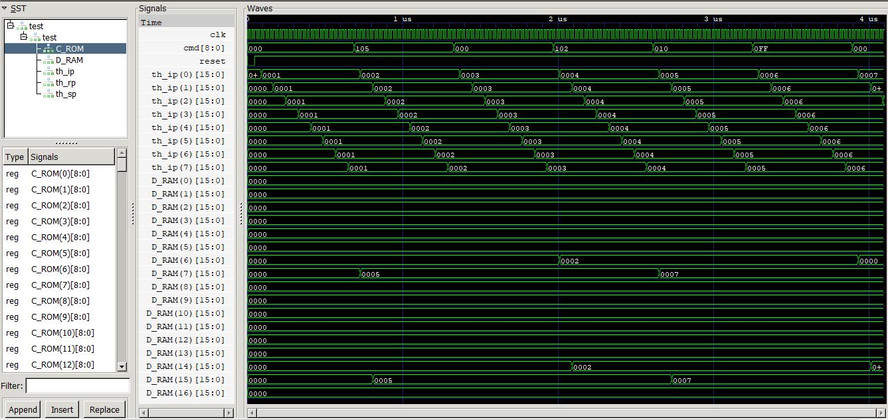

Приведен пример реализации многопоточного форт-процессора на языке Python при помощи инструментария MyHDL. Стековая архитектура процессора выбрана из-за ее интересного свойства – это небольшой размер контекста потока. Поскольку роль регистров выполняет стек, при переключении на другой поток необязательно иметь полный комплект регистров общего назначения. Продемонстрирован простой маршрут быстрого прототипирования софт-процессора, позволяющий при незначительных затратах времени и вычислительных ресурсов протестировать логику на работоспособность. В ядро описанного софт-процессора входят переключатель состояний процессора, счетчик текущего потока, наборы указателей стеков и счетчика команд для каждого из потоков, регистры текущего контекста, память данных и программ. Сама микроархитектура ядра реализуется через ряд функций, отвечающих за генерацию последовательных схем. Счетчик состояний процессора реализуется просто – установка в ноль при сигнале сброса, иначе – инкремент на каждый такт.