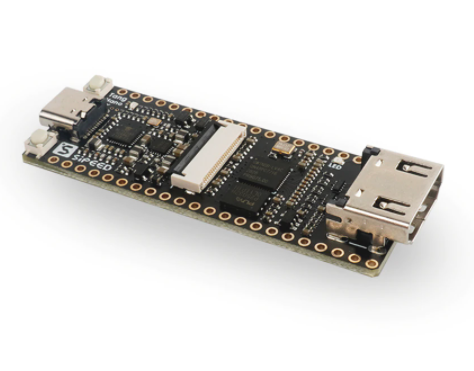

Отладочный модуль SmartLynq+ для Versal ACAP от Xilinx

Компания Xilinx добавила продукт в свой портфель модулей программирования, отладки и трассировки модуль SmartLynq+. Это высокоскоростной модуль отладки и трассировки, в первую очередь ориентированный на проекты, использующие платформу Versal, который значительно улучшает процесс конфигурации и скорость трассировки. Модуль SmartLynq+ обеспечивает до 28 раз более быстрое время загрузки Linux через высокоскоростной порт отладки (HSDP), чем через кабель передачи данных SmartLynq. Для захвата трассировки модуль SmartLynq+ поддерживает скорость до 10 Гбит/с через интерфейс HSDP. Это в 100 раз быстрее, чем стандартный JTAG. Более быстрые итерации и повторяющиеся загрузки повышают продуктивность разработки и сокращают цикл проектирования. Это означает снижение времени, затраченного на отладку, вместо которой вы можете сосредоточиться на запуске своих решений на основе Versal.

Преимущества модуля SmartLynq+:

- сверхбыстрая скорость загрузки, максимальная продуктивность разработки для более быстрых итераций

- высокоскоростная трассировка с улучшенной наглядностью, до 14 ГБ памяти трассировки для истории выполнения команд

- полная наглядность для гетерогенных архитектур, углублённая отладка для аппаратного IP и интеллектуальных механизмов (AI и DSP), адаптируемых механизмов и скалярных механизмов в Versal ACAP

- сплочённая и связанная со временем отладка всех подсистем

- гибкая и интеллектуальная платформа отладки с такими функциями, как интеллектуальная фильтрация и программируемый встроенный отладчик

- общая платформа отладки с единым представлением для удалённой многопользовательской среды.

Модуль SmartLynq+, обладающий революционной производительностью и наполненный умными функциями, является самым умным и гибким продуктом для отладки на рынке.

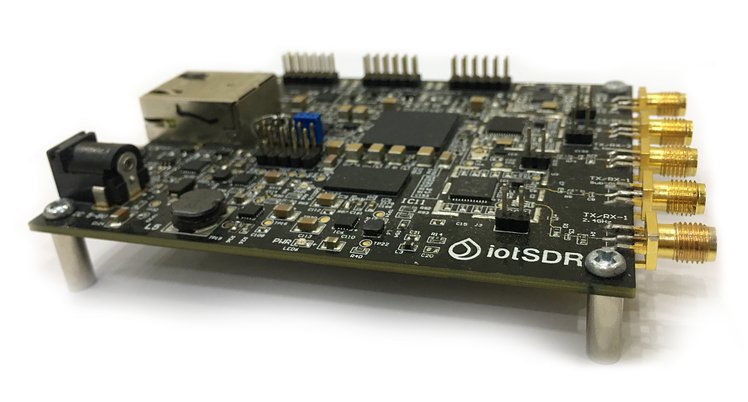

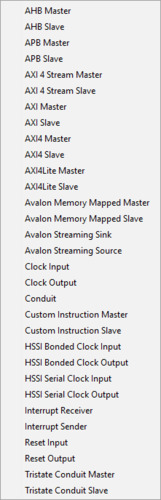

Основные характеристики и интерфейсы:

Основные функции и интерфейсы для модуля SmartLynq+:

- разъём USB 3.0 на стороне хоста, Gigabit Ethernet для подключения к сети и обеспечения удалённого доступа

- высокоскоростной порт отладки (HSDP) для более быстрого программирования, отладки и высокоскоростной последовательной трассировки

- JTAG (разъём PC4), обеспечивающий скорость до 100 МГц

- 8-битный порт ввода/вывода общего назначения (GPIO) для различных основных операций ввода/вывода на целевой плате

- разъём Mictor-38 для параллельной трассировки (зарезервирован для использования в будущем).

Аксессуары, поставляемые с модулем SmartLynq+, включают блок питания, кабели USB и Ethernet, карту памяти micro SD, кабели JTAG и GPIO. Пользователи должны загрузить последний образ SD-карты, выполнить необходимые шаги для настройки модуля, а затем приступить к разработке с помощью Versal ACAP. Учебник по встроенному дизайну (EDT) доступен пользователям, чтобы помочь им начать работу. Пользователи могут легко применять модуль SmartLynq+ с комплектами отладочных плат VCK190 Versal AI Core series и VMK180 Versal Prime series и испытать силу HSDP.