Реализация глубоких нейронных сетей на ПЛИС

Разработка приложений для глубокого обучения, компьютерного зрения, обработки сигналов и их развертывание на ПЛИС, графических процессорах или таких платформах, как Xilinx Zynq™, NVIDIA® Jetson или ARM®, является сложной задачей из-за ограничений ресурсов, присущих встроенным устройствам.

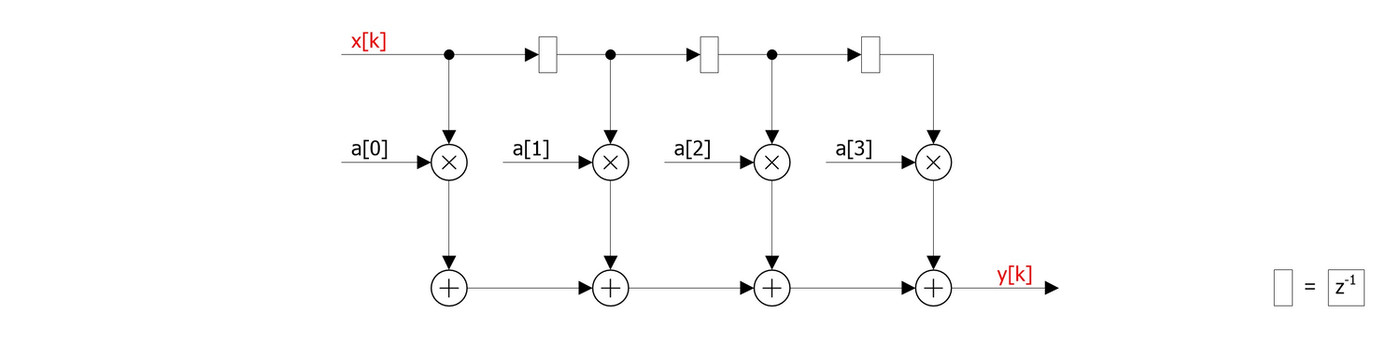

В процессе вебинара вы познакомитесь с рабочим процессом развертывания алгоритмов и приложений из MATLAB при помощи автоматической генерации кода C/C++, CUDA® или VHDL.

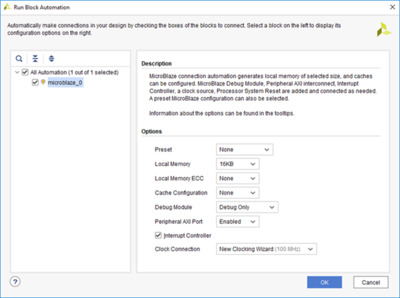

Для разработчиков систем, стремящихся интегрировать глубокое обучение в свои приложения на базе ПЛИС, мы расскажем о проблемах и соображениях развертывания на ПЛИС, а также подробно опишем рабочий процесс в MATLAB. Мы кратко покажем, как исследовать и прототипировать обученные сети на ПЛИС с использованием предварительно собранного битового потока из MATLAB. Вы можете дополнительно настроить свою сеть в соответствии с вашими требованиями к производительности и использованию аппаратных ресурсов, создать HDL-код и интегрировать его в проект на основе FPGA.

Вебинар состоится 10 ноября в 11:00