Решаем проблему разбиения чисел на PYNQ

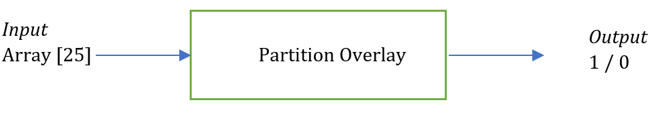

Многие математические задачи являются вычислительно затратными. А как мы знаем - где есть проблема с вычислительно затратными задачами - там найдется и место для FPGA. Вот собственно наткнулся на небольшой туториал: статью и видео, где решается проблема разбиения числа. Решается она с использованием PYNQ и оверлеем, написанным на HLS. По словам автора, он пытался решить задачу для набора из 25 чисел, но написанная программа на Python потребляла для получения ответа неприемлемо большое количество времени, поэтому он решил все это дело ускорить на FPGA. Звучит вполне интересно, предлагаю Вам ознакомиться с его руководством и видео.

А какие математические задачи Вы пытались решить на FPGA и пытались ли когда-нибудь в принципе это сделать? Напишите в комментах