Vivado 2019.2

Доступна для скачивания новая версия Vivado 2019.2

Что нового?

| Общее | Интеграция | Имплементация | Верификация |

| ОС/Поддержка новых устройств | SysGen/Model Composer | Синтез и имплементация | Моделирование |

| Установка и лицензирование | IP Integrator | Мощность | Отладка |

| Усовершенствование IDE | Улучшения IP | Частичная реконфигурация | Программирование |

Поддержка новых устройств

Добавлена поддержка следующих устройств:- Virtex UltraScale+ HBM:- XCVU31P, XCVU33P, XCVU35P, XCVU37P

Установка и лицензирование

- Представлен новый вариант установщика Xilinx Unified Installer для более лёгкой установки инструментов от компании Xilinx. Общий установщик позволяет установить пользователям ПО Xilinx, такие как Vitis, Vivado, локальную установку для развёртывания в облаке, Bootgen, Lab Edition, Hardware Server и Document Navigator

Усовершенствование IDE

- Новое поколение линтера для текстового редактора (основано на Sigasi)

- Улучшена проверка синтаксиса

- Автодополнение

- Переход к объявлению

- Поиск включений

- Автоформатирование / формирование отступов

- Включение через настройки проекта

Model Composer

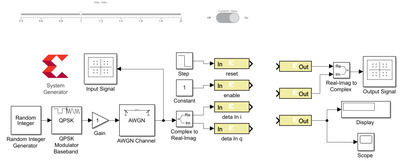

- Улучшена поддержка работы с векторами сигналов: улучшение в генерации кода для управления векторами из [N] сигналов, приводящая к повышению производительности.

- Усовершенствование блока Constant для параметров, заданных в виде вектора: блок Constant теперь поддерживает интерпретацию параметров, заданных в виде одномерного вектора, аналогично как блок Constant в Simulink

- Новые примеры проектов с оптимизацией DSP блоков:

- Реконструкция изображений МРТ при использовании 2D-БПФ

- Разработка низкочастотного фильтра с использованием блока FIR

- Сглаживающий фильтр изображения с использованием блока FIR

- Улучшение экспорта С/С++ функций: улучшен вывод сообщений об ошибках в окне Diagnostic Viewer

- Настройка свойств IP блоков для их экспорта в IP каталог: доступно указание свойств экспортируемого IP: имя. версия, язык (VHDL или Verilog)

- Поиск целевого устройства в Devise Chooser: быстрый поиск целевого устройства или платы по множеству критериев

- FIR блок поддерживает многоканальную обработку: поддержка обработки столбцов входящего сигнала в качестве независимых каналов данных для операций многоканальной фильтрации

- Поддерживаемые версии Matlab: R2018a, R2018b, R2019a и R2019b

IP Integrator

- Versal поддерживает и блокирует автоматизацию для GT wizard с IPs. Позволяет смешивать IP-протоколы в GT Quad.

- Скрыть или окрасить цепи/ блоки для лучшей видимости на блок-схеме?

Улучшения IP

- Улучшен SmartConnect

- Новая оптимизация по площади для маленьких конфигураций

- поддержка топологии LinkBlaze

- Доступна модель на языке SystemC

- URAM Readback/Writeback IP для устройств UltraScale+

- Решена проблема к доступу данных в URAM для отладки

- Появилась возможность инициализации

- HBICAP

- Позволяет встроенным процессорам получать доступ к конфигурационной памяти FPGA через внутренний порт доступа к конфигурации (ICAPEx)

- Дает пользователям возможность изменять функциональность схемы во время работы

- FIR Compiler

- Оптимизация под новые возможности DSP58 архитектуры Versal

- Дискретное преобразование Фурье (DFT)

- Улучшения для 5G

- Поддержка всех размеров выборки для удовлетворения требованиям 38.211

- Релиз асинхронного режима работы (по запросу)

- LTE Downlink Channel Encode

- исправление ошибок: некорректное поведение в случае снятия сигнала tvalid

- IP для работы с видео и изображениями

- MIPI DSI TX: добавлена поддержка 2.5Gb/s DPHY и DCS long packet

- MIPI CSI RX: новая опция оптимизации по занимаемым ресурсам

- Пример готового решения для Spartan SP 701 MIPI CSI RX to DSI TX

- DisplayPort Subsystems: пример реализации HDCP2.2

- Поддержка подсистемы SDI и YUV 444

Синтез RTL

- Поддержка виртуальных интерфейсов в SystemVerilog

- Расширена поддержка VHDL

- Поддержка физического типа TIME

- Более быстрая компиляция функций

- Улучшено управление ошибками

- XPM_MEMORY

- Асинхронный сброс выходного регистра в несимметричной RAM

- Поддерживается для обоих типов памяти: Block RAM и UltraRAM

- Разрешена оптимизация модулей с пинами, отмеченными как MARK_DEBUG

- Ранее было возможно при атрибуте DONT_TOUCH

- Разрешено сопоставление ретайминга control sets регистровых конвейеров на сдвиговые регистры (SRL)

Имплементация

- Dynamic Function eXchange (DFX)

- Частичная реконфигурация (Partial Reconfiguration (PR)) является частью общего решения DFX

- DFX включает: возможности устройств, маршруты проектирования в Vivado, IP для частичной реконфигурации и многое другое

- Распространяется на все архитектуры: от 7-ой серии до Versal

- Новый функционал в будущих релизах

- Читайте подробнее здесь

- AXI High-Bandwidth ICAP interface IP

- Поддержка чтения и записи по AXI до 256 пакетов за транзакцию

- Дополнительный интерфейс мастер AXI4-Stream для чтения с неограниченной длиной пакета за транзакцию

- Memory mapped AXI4 слэйв интерфейс

- Поддержка записи и чтения размером до 230 байт?

- Подробнее в PG349

- Частичная реконфигурация (Partial Reconfiguration (PR)) является частью общего решения DFX

- Этап имплементации

- Опция PhysOpt теперь включена по умолчанию в стратегии Vivado Implementation Defaults

- Новая директива Default опции phys_opt

- Меньше оптимизированных путей, чем в предыдущих версиях?

- Сосредоточена на решении временных выбросов

- Очень быстрое выполнение

- LUT combining optimization добавлена в "Physical-Synthesis-in-Placer" (PSIP)?

- Новая оптимизация для путей, содержащих BUFG/CE в опции opt_design

- Уменьшают набег фазы тактового сигнала для удовлетворения временных ограничений проекта

- Анализ и достижение заданных временных ограничений проекта

- Стратегия предсказания RQS (report qor (Quality of results) suggestions)

- Использует ИИ для предсказания 3-х лучших стратегий имплементации

- report_qor_suggestions -strategy

- RQA (report_qor_assessment)?

- Содержит рекомендации по использованию стратегий инкрементной компиляции и стратегии имплементации RQS

- Добавляет сводку report_failfast для отслеживания проблем проектирования перед импелементацией?

- Новая метрика перегруженности: добавлена визуализация уровня перегрузки соединений (Windows -> Metrics)?

- Команда report_ram_utilization дополнена отчётом о LUTRAM

- Новая UltraFast методология для проверки небезопасных путей пересечения тактовых доменов (CDC) между MMCM

- Стратегия предсказания RQS (report qor (Quality of results) suggestions)

- Инкрементная компиляция

- Дерективы инкрементной имплементации

- Quick: самое быстрое выполнение, минимальные усилия достижения временных ограничений

- RuntimeOptimized: быстрое выполнение при сохранении временных ограничений

- TimingClosure: пытается достичь временных ограничений

- Не нужно изменять директивы размещения и трассировки

- Среда автоматически решает какой вариант имплементации запустить: инкрементную или по умолчанию с исходными директивами

- Улучшены результаты, достигаемые с помощью опции phys_opt_design при инкрементной имплементации

- Более точная оптимизация

- Улучшено переиспользование предыдущих результатов размещения и трассировки

- Инкрементный синтез: повторное использование предыдущих результатов теперь учитывает изменения в параметрах synth_design

- Дерективы инкрементной имплементации

Vivado Simulator

-

Моделирование

- Поддержка UVM 1.2 в Vivado Simulator (XSIM), позволяющую пользователям создавать высококачественную среду верификации с помощью тестбенчей на основе UVM