Заметка: FPGA уходит в софт или как изменился маршрут проектирования для ПЛИС

В LinkedIn появилась небольшая заметка от одного из ведущих руководителей направления высокоуровнего синтеза в компании Xilinx - Frederic Rivoallon, рассказывающая нам о "мягкой" стороне проектирования на FPGA.

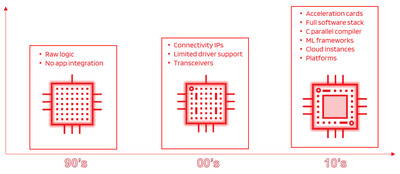

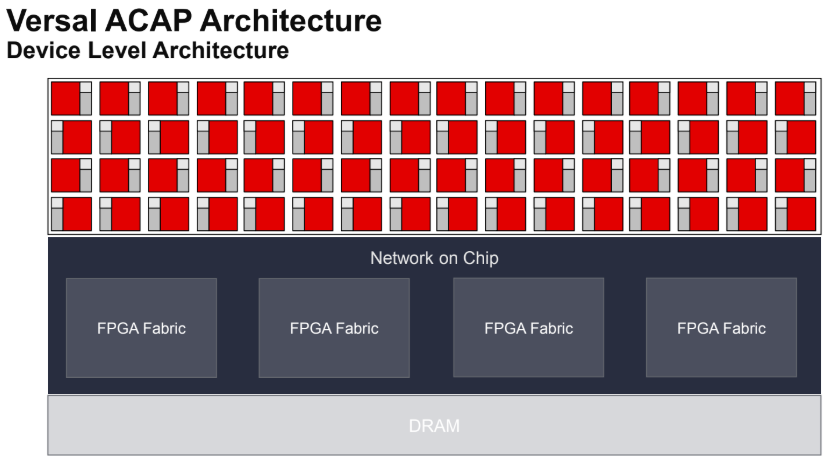

Маршрут проектирования для FPGA уже не будет прежним. Сейчас всё больше и большее внимание крупных производителей сосредоточено именно на высокоуровневом синтезе, благодаря чему у нас появляется возможность проектировать на ПЛИС не только стандартными низкоуровневыми средствами RTL, но и с использованием С/С++/SystemC/OpenCL/python, а также различных фреймворков TensorFlow/Caffe/Keras и др.

Кому-то такой подход ближе, кто-то не стесняется своих эмоций и с негативом высказывается за такой подход. Тем не менее, имеем то, что имеем. Предлагаем Вам ознакомиться с заметкой более подробно.

PS: возможно потребуется регистрация в LinkedIn

PS2: А Вы слышали, что один энтузиаст делает свой синтезатор с C#-to-RTL? Подробнее о его проекте здесь, а обсудить эту идею можно здесь