FPGA Daily News #035

Did you miss this FPGA news 24-Mar-2022 ?

- GitHub - ARIES-Embedded/riscv-on-max10: Reference designs and firmware for open-source RISC-V core implementation on MX10 and SpiderSoM

Reference designs and firmware for open-source RISC-V core implementation on MX10 and SpiderSoM - GitHub - ARIES-Embedded/riscv-on-max10: Reference designs and firmware for open-source RISC-V core ...

- MicroZed Chronicles: Xilinx Power Management Libraries (XilPM)

Both the AMD-Xilinx MPSoC and Versal ACAP families have complex internal power structures which consists of domains like the Full Power Domain (FPD) or Low Power Domain (LPD), Islands such as individual processors, nodes such as peripherals, and memories. These domains and islands can be powered up or down to optimize the power dissipation of the overall solution. This allows for dynamic power management at run time and enables the most power-efficient implementation for current use cases. In bo

- infobit iWall 409R

The iWall 409R is a 4K Ultra HD video wall controller designed by INFOBIT AV. Supports 4x HDMI inputs (1x 4K@60Hz, 3x 4K@30Hz), 1x DP input (4K@60Hz), 9x HDMI outputs (1080p@60Hz), and 1x DP loop out.

- QuickLogic Delivers eFPGA IP for TSMC 22nm Process from Australis IP Generator - EE Times Asia

QuickLogic has launched its first customer-defined eFPGA block targeting TSMC's 22nm process node.

- Instigate Semiconductor | Senior FPGA Logical Verification Engineer | Vanadzor branch (EN-ENj59082)

Instigate Semiconductor CJSC recruits Senior FPGA Logical Verification Engineer in Vanadzor.

- Raytheon Intelligence and Space - Cleared FPGA - Hiring Event

Raytheon Intelligence & Space delivers the disruptive technologies our customers need to succeed in any domain, against any challenge.

- Intel Fuels FPGA Innovation with Acceleration Development Platform Strategy

Intel’s development strategy for FPGA-based acceleration cards – powering data centers, networking, and telecommunications – enables rapid development and deployment of production-ready acceleration solutions based on Intel’s latest, fastest, and most powerful FPGAs. The new ecosystem-centric strate...

- (4) Q&A: What's Implemented in the Hard Logic in Achronix Speedster7t FPGAs? - YouTube

Question: What’s implemented in the hard logic in Achronx Speedster7t FPGAs? And how can developers integrate their own capabilities around the fabric? Answe...

- Webinar "Hello FPGA - Getting Started with Microchip FPGAs" - завершена

- What are Full-Custom and Semi-Custom VLSI Designs?? | by Radha Kulkarni | Mar, 2022 | Medium

— — VLSI Design Methodology can be broadly divided into 2 types:

- Wendler Márk: PolarFire SoC

- Mutal primes and recursion - a different kind of FPGA adventure | LinkedIn

- Lab Workshop ‘FPGA Architecture and Programming using Verilog HDL – NPTEL+

- Intel FPGA | Macnica Americas

Leading FPGA, SoC and Power Products Altera® operates as the Programmable Solutions Group (PSG) within Intel Corporation (NASDAQ: INTC), following its acquisition by Intel in 2015. Altera’s programmable solutions enable designers of electronic systems to rapidly and cost effectively innovate, differentiate and win in their markets. Altera offers FPGAs, SoCs, CPLDs, and complementary technologies, such as power converters, to provide high-value solutions to customers worldwide.

- Optimize FPGA and ASIC Speed and Area Using HDL Coder - MATLAB & Simulink

- Lattice to Showcase Low Power FPGA-based AI/ML Solutions at tinyML Summit 2022 | Business Wire

Lattice Semiconductor (NASDAQ: LSCC), the low power programmable leader, today announced that it will showcase the capabilities of its Lattice sensAI™

- Intel axes older FPGA cards, moves development to customers • The Register

If you want your own custom SmartNIC, knock yourself out, says x86 giant

- GitHub - Hahn-Schickard/AutoFlow: Bring your AI to the Edge - Starting from building the ML model to the selection of the target platform to the optimization and implementation of the model on the target platform.

Bring your AI to the Edge - Starting from building the ML model to the selection of the target platform to the optimization and implementation of the model on the target platform. - GitHub - Hahn-S...

- Just What is an FPGA, Anyway? | The Ojo-Yoshida Report

Neither programmable nor an array of gates, FPGAs can sometimes go where ASICs fear to tread.

- Menta Announces Joint Partnership with Trusted Semiconductor Solutions | SemiWiki

The newly formed partnership will provide US defense customers access to the most flexible, adaptable, made-to-order eFPGA technology, licensed by Menta and made in the USA by Trusted Semiconductor Solutions New York, March 21, 2022 – Today, Menta, the proven eFPGA pioneer and Trusted...

- CAES Introduces Family of Radiation Hardened NOR Flash Memories for Space FPGAs | CAES

CAES introduced today a line of RadHard NOR Flash Memory devices that uniquely deliver the boot-memory densities required by microprocessors and FPGAs used in space applications.

- Use Tensil and PYNQ to run ResNet-20 on Ultra96 FPGA board - Hackster.io

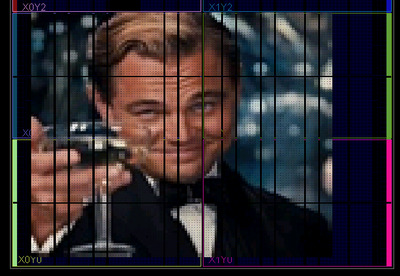

Show how to use Tensil’s open-source accelerator and Xilinx PYNQ to run ResNet-20 model on Avnet Ultra96 development board. By petrohi.

- PRODUCT OF THE WEEK: Abaco Systems’ SOSA aligned, FPGA processing card with Xilinx Zynq UltraScale+ MPSoC technology - Military Embedded Systems

This week’s product, the Abaco Systems’ VP831 3U FPGA processing card with 100 gigabit Ethernet, leverages Xilinx Virtex UltraScale+ and Zynq UltraScale+ technology. A technology upgrade from the existing VP889 product, the VP831 is aligned with the Sensor Open Systems Architecture (SOSA) Technical Standard and is designed for mission-critical military applications such as communications, sensor processing, radar, and electronic warfare.

- Silex Insight Launches DDR Encrypter for High-Performing Systems (ASIC/FPGA) - Embedded Computing Design

Silex Insight, a provider of cryptographic IP solutions, is now extending their offering by launching a high throughput DDR encrypter (100Gbps).

- lochsh

- FPGA Community

Learn about the FPGA Community, its benefits, and how you can join.

- Field Programmable Gate Array (FPGA) in Cyber Security Market 2022-2030, By Top Key Players – QuickLogic Corp., Intel Corporation, Microchip Technology Inc., Texas Instruments Incorporated, Cypress Semiconductor Corporation, Teledyne Technologies Incorporated – ChattTenn Sports

- Silex introduces new solution to accelerate cryptographic operations on FPGA or ASIC » CryptoNinjas – Dailywire

Silex Insight, a provider of cryptographic IP solutions, announced today it is now extending its offering by introducing a Network Security Crypto Accelerator.The Network Security Crypto Accelerato…

- RISC-V - Mouser Electronics

RISC-V is a new open source instruction set architecture available in both 32-bit and 64-bit word lengths. This topic will delve into the architecture, feature set, and available software toolchain to use for RISC-V development as well as featuring two case studies using RISC-V in a Linux environment and a RISC-V Gateway design.

- Silex introduces new answer to speed up cryptographic operations on FPGA or ASIC - IND News Reporter

- Silex introduces new answer to speed up cryptographic operations on FPGA or ASIC IND News Reporter Latest News Report

- RVfpga (RISC-V fpga) Understanding Computer Architecture Workshop-May 20th Tickets, Fri 20 May 2022 at 09:00 | Eventbrite

Teaching Computer Architecture? Give us a day of your time, and we will set you up to teach with RISC-V, the fastest growing new ISA

- Enclustra FPGA Solutions | Mercury+ XU6 | Xilinx Zynq UltraScale+ MPSoC Module | System-on-Chip (SoC) Module | System-on-Module (SOM) | ZU2CG | ZU2EG | ZU3EG | ZU4CG | ZU4EV | ZU5EV

The Enclustra Mercury+ XU6 System-on-Module (SOM) is optimized for high I/O count applications. It has 294 user I/Os and is based on the Xilinx Zynq UltraScale+ MPSoC. The module is equipped with up to 8 GByte of fast DDR4 SDRAM. Also included are up to 8 6/12.5 Gbps MGTs and all common standard interfaces. Thanks to its 6 available product models, it covers a wide range of applications.

- Events | XACC Resources

XACC Resources

- Machine Learning | Softnautics

Softnautics is a Machine Learning Development Company providing next-gen machine learning solutions that help businesses to reach new heights.

- Reflex CES décline une version industrielle de son module-système COM Express doté d'un FPGA Stratix 10

Reflex CES décline une version industrielle de son module-système COM Express doté d'un FPGA Stratix 10

- RapidSilicon | Welcome to the FPGA Revolution!

- 5G Blitz Week | Achronix Semiconductor Corporation

Join Achronix online at 5G Blitz Week to hear the latest in 5G deployments, the opportunities in new sectors such as manufacturing and a glance ahead to the promise of THz spectrum for 6G deployments. Find out how Achronix's Speedster®7t FPGA architecture enables developers to quickly respond to the rapidly changing 5G landscape and emerging 6G standard.

- 1.0 Riviera-PRO™ Overview: Advanced Verification Platform - Demonstration Videos - Multimedia - Resources - Support - Aldec

Riviera-PRO™ addresses verification needs of engineers crafting tomorrow's cutting-edge FPGA and SoC devices.

- Zoom

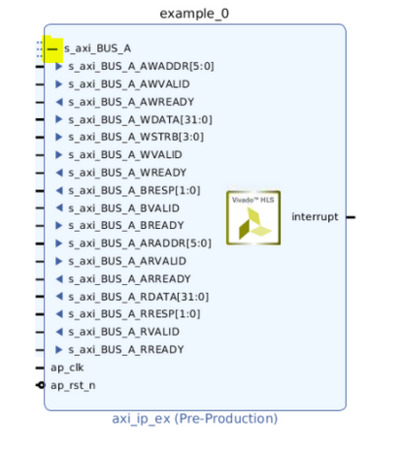

Background: Imagine a situation where with traditional flow a functional regression which takes 3 months of time using 1000 CPU gets completed in just 3 days by using even less resources say by using just 1 CPU instead 1000 CPU. Sounds amazing right? Well, it's possible by raising the level of abstraction of your IC design. It has been done adopting a C++ High level synthesis flow using Catapult with significant cost reduction by reducing development effort by 40% and design time by 50%. What is HLS? High-level synthesis (HLS), sometimes referred to as C synthesis, electronic system-level (ESL) synthesis, algorithmic synthesis, or behavioral synthesis, is an automated design process that takes an abstract behavioral specification of a digital system and find a register-transfer level structure that realizes the given behavior. Designing in SystemC or C++, applying High-Level Synthesis (HLS), and achieving quality of results (QoR) comparable to handwritten RTL is often met with much scepticism by design engineers and project management, even with countless success stories of HLS in multiple application domains. In this webinar, we will present the workflow of Catapult HLS, with the focus on step-by-step generation of optimized RTL from C. Who Should Attend? • RTL designers, • Hardware architects • Managers • Project Managers Post the session, the participants will be able to • Learn Step-by-step generation of optimized RTL from C • Understand basic HLS transformations work • Know workflow of Catapult® HLS • Know how the advanced analysis capabilities within the Catapult® HLS platform can be used to give the design engineer full control of the HLS process to achieve both productivity and QoR Happy Learning, PROLIM India Team