Новостной дайджест событий проекта: Январь 2021

ПЛИСкульт привет, FPGA комьюнити.

Мы продолжаем держать вас в курсе последних событий из мира программируемой логики и решили немного пересмотреть формат дайджеста. Мы добавили категории, чтобы было проще искать информацию. В этот выпуск мы добавили: вебинары, анонсы, статьи, стримы, вакансии и даже сделали pdf версию. Подробности по катом

Содержание:

- Вебинары, семинары

- Анонсы

- Новинки изделий на FPGA

- Статьи, заметки на буржуйском

- Статьи, заметки на русском

- Стримы

- Вакансии

Вебинары, семинары

Microchip PolarFire® SoC FPGA - часть 4 :: Компания Microchip подготовила серию вебинаров о работе с PolarFire® SoC FPGA, которая имеет аппаратный RISC-V. В 4-ом вебинаре серии речь пойдет о работе с Hart Software Services (HSS) и как оно применяется при разработке на PolarFire.

Microchip PolarFire® SoC FPGA - часть 4 :: Компания Microchip подготовила серию вебинаров о работе с PolarFire® SoC FPGA, которая имеет аппаратный RISC-V. В 4-ом вебинаре серии речь пойдет о работе с Hart Software Services (HSS) и как оно применяется при разработке на PolarFire.

Повышение производительности систем на базе FPGA за счёт оптимизации архитектуры памяти :: Компания MoSyS, предлагающая решения по внешней памяти, проводит вебинар, на котором вы узнаете как архитектура и организация памяти разрабатываемой системы на базе ПЛИС, , влияет на пропускную способность системы, производительность, затраты и время проектирования.

Повышение производительности систем на базе FPGA за счёт оптимизации архитектуры памяти :: Компания MoSyS, предлагающая решения по внешней памяти, проводит вебинар, на котором вы узнаете как архитектура и организация памяти разрабатываемой системы на базе ПЛИС, , влияет на пропускную способность системы, производительность, затраты и время проектирования. 424 бесплатных тренинга от Intel FPGA :: До второго квартала 2021 года вы можете воспользоваться бесплатными учебными курсами Intel® FPGA, доступными онлайн. В настоящее время в списке 424 тренинга, так что вы обязательно найдете что-то полезное .

424 бесплатных тренинга от Intel FPGA :: До второго квартала 2021 года вы можете воспользоваться бесплатными учебными курсами Intel® FPGA, доступными онлайн. В настоящее время в списке 424 тренинга, так что вы обязательно найдете что-то полезное . Xilinx Versal ACAP - от ПЛИС к платформе :: С семейством Versal ACAP Xilinx вводит совершенно новую архитектуру, позволяющую эффективно использовать широкий спектр гетерогенных вычислительных ресурсов. Этот вебинар посвящен основным концепциям семейства и знакомит с вычислительными механизмами, APU (Arm A72) и RPU .

Xilinx Versal ACAP - от ПЛИС к платформе :: С семейством Versal ACAP Xilinx вводит совершенно новую архитектуру, позволяющую эффективно использовать широкий спектр гетерогенных вычислительных ресурсов. Этот вебинар посвящен основным концепциям семейства и знакомит с вычислительными механизмами, APU (Arm A72) и RPU . Intel FPGA Technology Day EMEA :: На этом однодневном мероприятии компания Intel расскажет об использовании ПЛИС в передовых технологиях и решениях для индустрии 4.0. Слушателей ожидает более 100 единиц контента, большинство из которых будет длиться по 20 минут. Все материалы будут доступны в течение 4-х недель после мероприятия

Intel FPGA Technology Day EMEA :: На этом однодневном мероприятии компания Intel расскажет об использовании ПЛИС в передовых технологиях и решениях для индустрии 4.0. Слушателей ожидает более 100 единиц контента, большинство из которых будет длиться по 20 минут. Все материалы будут доступны в течение 4-х недель после мероприятия QuickSilicon зимний хакатон :: Зимний хакатон начался! Начните прямо сейчас и получите шанс выиграть интересные призы!

QuickSilicon зимний хакатон :: Зимний хакатон начался! Начните прямо сейчас и получите шанс выиграть интересные призы!  Многодневный семинар: Xilinx Adapt - Automotive Компания Xilinx проводит серию бесплатных многодневных семинаров под общим названием Xilinx.Adapt В третьем из 5-ти семинаров, который пройдёт с 12-14 января 2021, будут рассмотрены инновационные решения компании Xilinx в сегменте Automotive.

Многодневный семинар: Xilinx Adapt - Automotive Компания Xilinx проводит серию бесплатных многодневных семинаров под общим названием Xilinx.Adapt В третьем из 5-ти семинаров, который пройдёт с 12-14 января 2021, будут рассмотрены инновационные решения компании Xilinx в сегменте Automotive.

Анонсы

ИИ в дата-центре: использование возможностей ПЛИС :: В последние несколько лет машинное обучение (ML) стало наиболее перспективным методом извлечения значимых паттернов из данных. Этот радикально новый тип ИТ-нагрузки создает гораздо более интеллектуальные программные системы, но создает серьезные проблемы для традиционной инфраструктуры центров обработки данных.

ИИ в дата-центре: использование возможностей ПЛИС :: В последние несколько лет машинное обучение (ML) стало наиболее перспективным методом извлечения значимых паттернов из данных. Этот радикально новый тип ИТ-нагрузки создает гораздо более интеллектуальные программные системы, но создает серьезные проблемы для традиционной инфраструктуры центров обработки данных. Gowin объявляет о доступности ПЛИС автомобильного класса :: Стандарт AEC-Q100 существует уже более 20 лет, определяя квалификационные требования к надежности автомобильных интегральных схем. Чтобы получить сертификат, соответствующий требованиям AEC-Q100 Grade 2, производитель должен представить продукт, способный работать в экстремальных условиях.

Gowin объявляет о доступности ПЛИС автомобильного класса :: Стандарт AEC-Q100 существует уже более 20 лет, определяя квалификационные требования к надежности автомобильных интегральных схем. Чтобы получить сертификат, соответствующий требованиям AEC-Q100 Grade 2, производитель должен представить продукт, способный работать в экстремальных условиях.

Компания Xilinx выпустила новый релиз Vitis AI за номером 1.3. :: Среда разработки Vitis ™ AI - это продукт для реализации приложений искусственного интеллекта на аппаратных платформах Xilinx, как на оконечных устройствах, так и на ускорительных картах Alveo ™ .

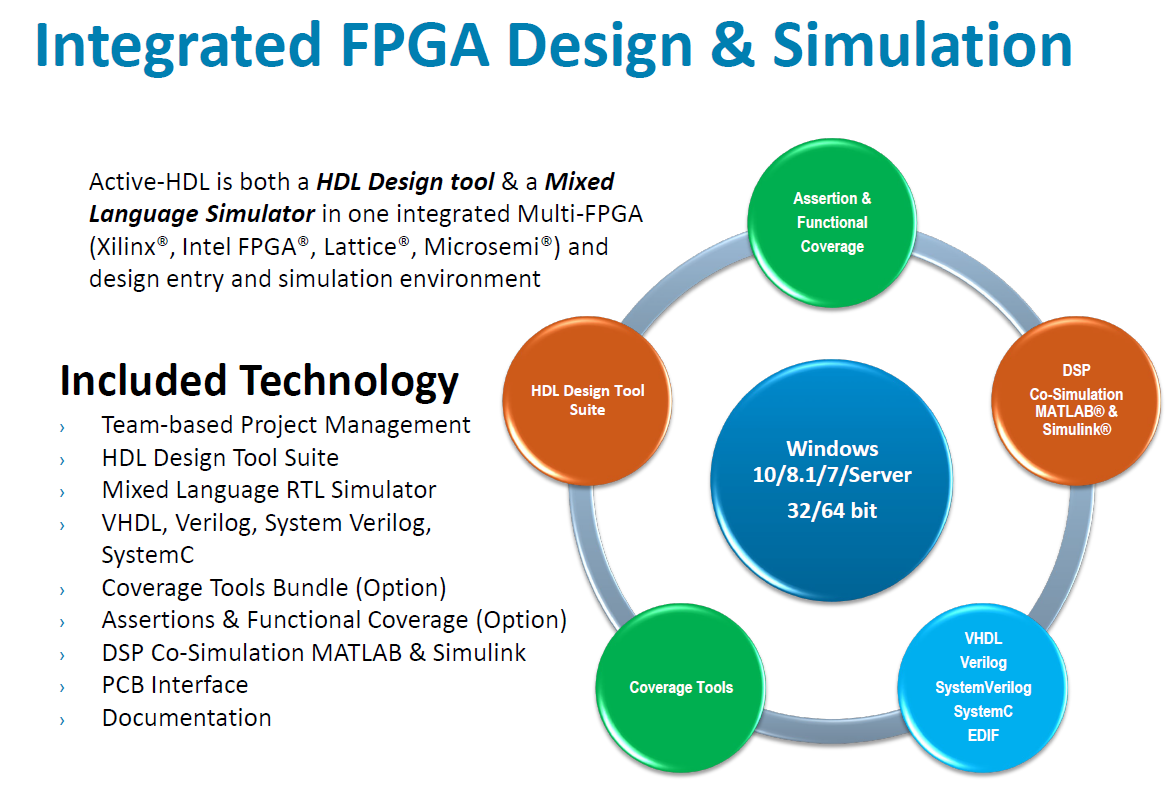

Компания Xilinx выпустила новый релиз Vitis AI за номером 1.3. :: Среда разработки Vitis ™ AI - это продукт для реализации приложений искусственного интеллекта на аппаратных платформах Xilinx, как на оконечных устройствах, так и на ускорительных картах Alveo ™ . Выпущен новый релиз симулятора ПЛИС Active-HDL 12.0! :: Компания ALDEC выпустила новый релиз симулятора ПЛИС Active-HDL 12.0! Active-HDL 12.0 позволяет разработчикам ПЛИС в полной мере использовать многие функции последней версии VHDL и помогает повысить эффективность проверки проекта .

Выпущен новый релиз симулятора ПЛИС Active-HDL 12.0! :: Компания ALDEC выпустила новый релиз симулятора ПЛИС Active-HDL 12.0! Active-HDL 12.0 позволяет разработчикам ПЛИС в полной мере использовать многие функции последней версии VHDL и помогает повысить эффективность проверки проекта .

Новые возможности симулятора Active-HDL 12 :: В новой версии симулятора ПЛИС Active-HDL v12, которая вышла в 2021 г., представлены следующие улучшения:

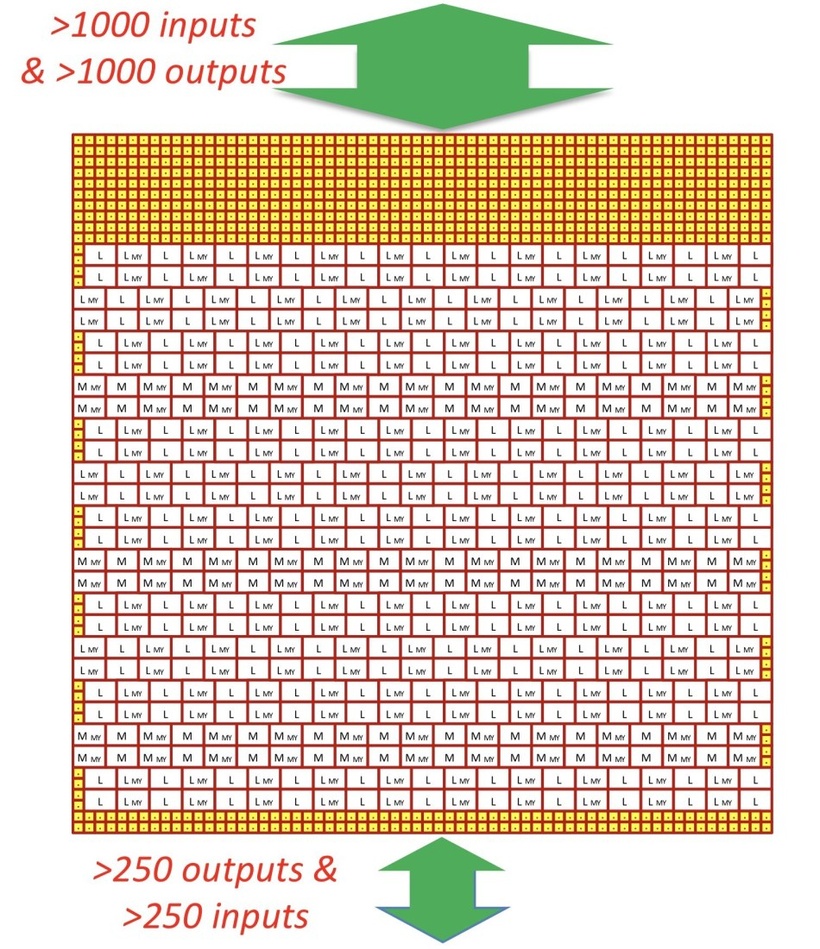

Новые возможности симулятора Active-HDL 12 :: В новой версии симулятора ПЛИС Active-HDL v12, которая вышла в 2021 г., представлены следующие улучшения: Intel анонсировала FPGA с интегрированными АЦП и ЦАП :: Компания Intel объявила о разработке FPGA с интегрированными АЦП и ЦАП с пропускной способностью 64GSPS. Интеграция преобразователей данных осуществляется по технологии EMIB .

Intel анонсировала FPGA с интегрированными АЦП и ЦАП :: Компания Intel объявила о разработке FPGA с интегрированными АЦП и ЦАП с пропускной способностью 64GSPS. Интеграция преобразователей данных осуществляется по технологии EMIB . Центр компетенций Lattice :: Компания Lattice открывает центр обучения и компетенций LEC2.

Центр компетенций Lattice :: Компания Lattice открывает центр обучения и компетенций LEC2.

Новинки изделий на FPGA

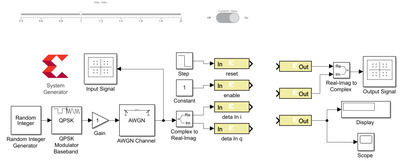

Open-source + VHDL + IEEE 802.11 = bladeRF :: bladeRF-wiphy - это программно-определяемый радиомодем с открытым исходным кодом совместимый с IEEE 802.11 и написанный на VHDL. Модем способен модулировать и демодулировать пакеты 802.11 (на основе протокола WiFi) и работать непосредственно с модулем bladeRF 2.0 micro xA9 .

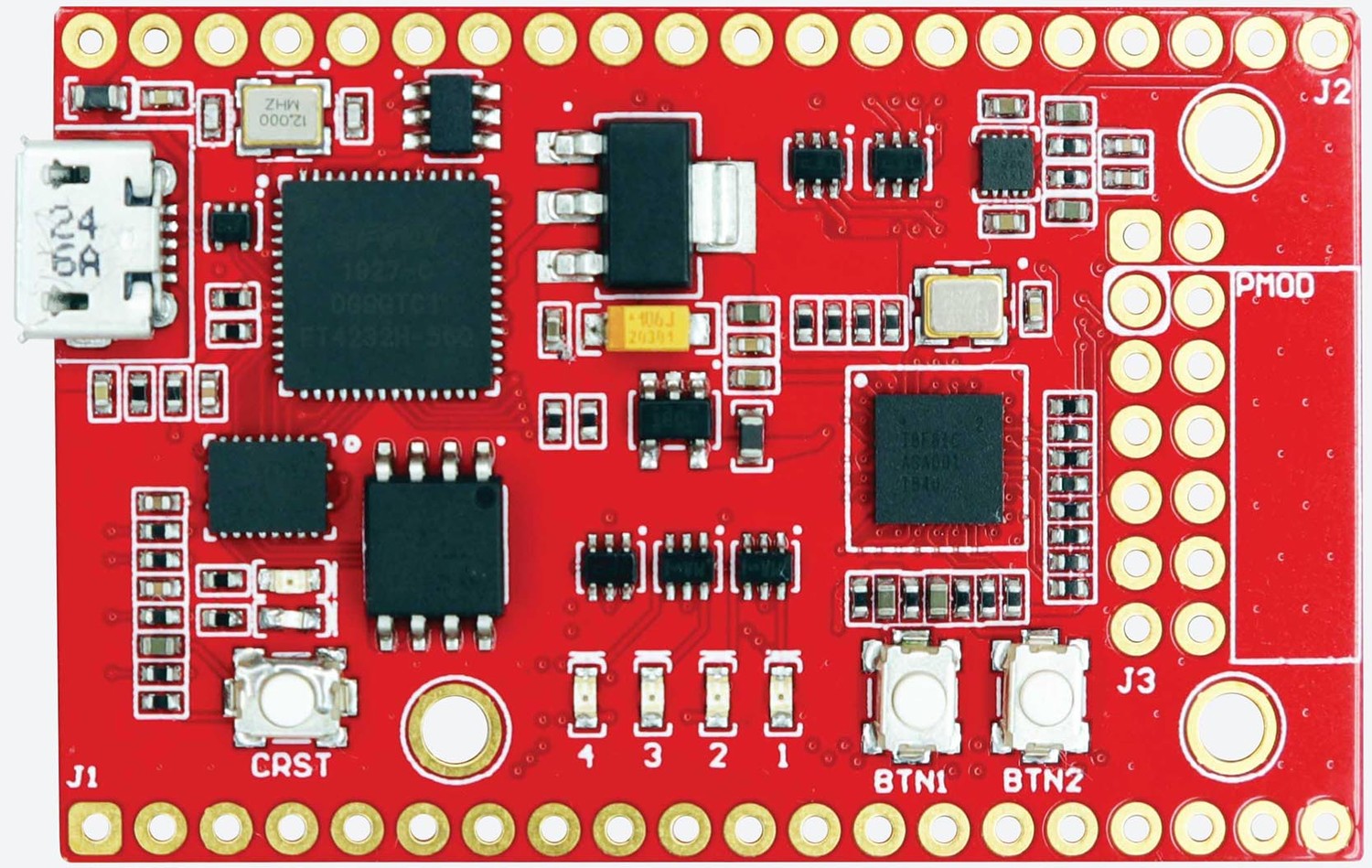

Open-source + VHDL + IEEE 802.11 = bladeRF :: bladeRF-wiphy - это программно-определяемый радиомодем с открытым исходным кодом совместимый с IEEE 802.11 и написанный на VHDL. Модем способен модулировать и демодулировать пакеты 802.11 (на основе протокола WiFi) и работать непосредственно с модулем bladeRF 2.0 micro xA9 . Xyloni - Отладочная плата на ПЛИС Efinix Trion T8 :: Отладочная плата Xyloni построена на базе ПЛИС Efinix® T8, имеющей 81-шариковый корпус FBGA. ПЛИС T8 имеют программируемую логику и структуру маршрутизации, построенную на технологии Efinix® Quantum™. Устройства T8 также включают встроенные блоки памяти, блоки умножения (или блоки DSP), PLL и генератор.

Xyloni - Отладочная плата на ПЛИС Efinix Trion T8 :: Отладочная плата Xyloni построена на базе ПЛИС Efinix® T8, имеющей 81-шариковый корпус FBGA. ПЛИС T8 имеют программируемую логику и структуру маршрутизации, построенную на технологии Efinix® Quantum™. Устройства T8 также включают встроенные блоки памяти, блоки умножения (или блоки DSP), PLL и генератор. Xilinx выпустил две отладки на ACAP VERSAL Компания Xilinx представила две новых отладочных платы на ACAP семейства Versal: Versal AI Core VCK190 и Versal Prime VMK180.

Xilinx выпустил две отладки на ACAP VERSAL Компания Xilinx представила две новых отладочных платы на ACAP семейства Versal: Versal AI Core VCK190 и Versal Prime VMK180.

Статьи, заметки на буржуйском

Поднимаем OpenCL :: В блоге Адама Тейлора похоже появляется новая ветка статей, которая будет связана с написанием OpenCL кода под различные целевые платформы. В частности, в первой статье Адам поднимает простой проект на OpenCL для ускорителя Alveo U50.

Поднимаем OpenCL :: В блоге Адама Тейлора похоже появляется новая ветка статей, которая будет связана с написанием OpenCL кода под различные целевые платформы. В частности, в первой статье Адам поднимает простой проект на OpenCL для ускорителя Alveo U50. Разбираемся в типах программных лицензий. Заметка от Synopsys :: Зачастую разработчики в своей работе используют готовые библиотеки, фреймворки, находят интересные решения на github или stack overflow и внедряют в свой продукт. Стоит иметь в виду, что используемый код идет с соответствующей лицензией, упоминание о которой вы легко можете найти в крупных репозиториях на github.

Разбираемся в типах программных лицензий. Заметка от Synopsys :: Зачастую разработчики в своей работе используют готовые библиотеки, фреймворки, находят интересные решения на github или stack overflow и внедряют в свой продукт. Стоит иметь в виду, что используемый код идет с соответствующей лицензией, упоминание о которой вы легко можете найти в крупных репозиториях на github. VHDL Style Guide :: VHDL Style Guide (VSG) предназначен для проверки и исправления VHDL исходников в соответствии с заданным стилем написания кода. VSG представляет собой набор библиотек, написанных на языке Python.

VHDL Style Guide :: VHDL Style Guide (VSG) предназначен для проверки и исправления VHDL исходников в соответствии с заданным стилем написания кода. VSG представляет собой набор библиотек, написанных на языке Python.  Компьютерное зрение на платфомре ZYNQ :: Brian ChengHe Wu предоставил исходный код и видео-инструкцию к своему проекту по работе с Компьютерным Зрением на платформе ZYNQ. По завершению курса вы сможете разработать устройство похожее на Kinect от Microsoft или Intel RealSense .

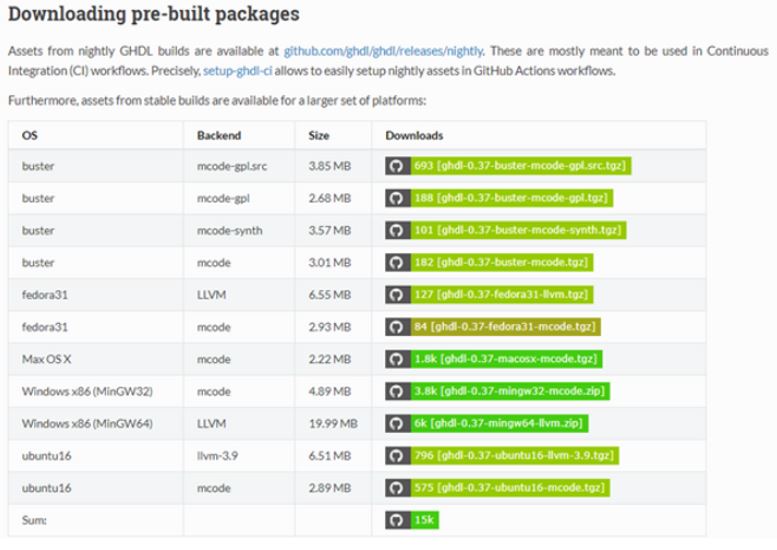

Компьютерное зрение на платфомре ZYNQ :: Brian ChengHe Wu предоставил исходный код и видео-инструкцию к своему проекту по работе с Компьютерным Зрением на платформе ZYNQ. По завершению курса вы сможете разработать устройство похожее на Kinect от Microsoft или Intel RealSense . Установка и работа с GHDL для верификации :: В блоге Адама тейлора появилось небольшое руководство по началу работы с симулятором с открытым исходным кодом GHDL. Этот симулятор предназначен для верификации проектов, написанных на VHDL .

Установка и работа с GHDL для верификации :: В блоге Адама тейлора появилось небольшое руководство по началу работы с симулятором с открытым исходным кодом GHDL. Этот симулятор предназначен для верификации проектов, написанных на VHDL .

Статьи, заметки на русском

UVM тест таблицы sin/cos :: В данном руководстве описывается пример построения тестового окружения с использованием UVM для проверки компонента, описанного при помощи HDL .

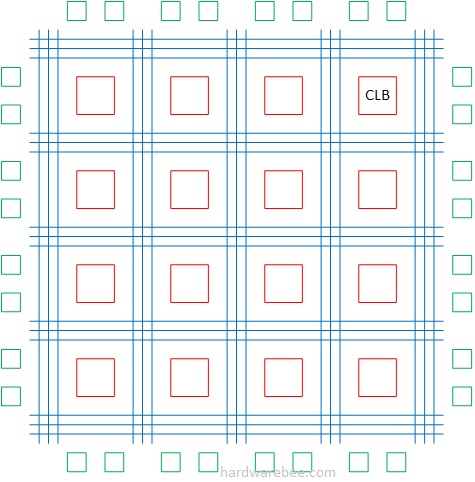

UVM тест таблицы sin/cos :: В данном руководстве описывается пример построения тестового окружения с использованием UVM для проверки компонента, описанного при помощи HDL . FPGA или микроконтроллер: что же выбрать? :: Ох уж эти бесконечные холивары! Вот вам еще одна небольшая заметка формата "за/против", но в разрезе программируемой логики и микроконтроллеров.

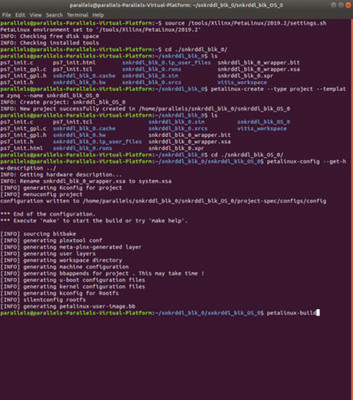

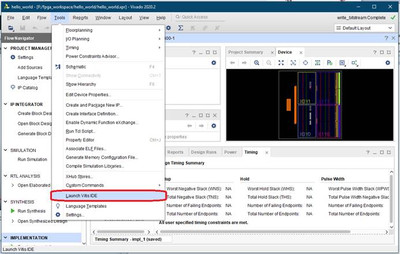

FPGA или микроконтроллер: что же выбрать? :: Ох уж эти бесконечные холивары! Вот вам еще одна небольшая заметка формата "за/против", но в разрезе программируемой логики и микроконтроллеров. ZYNQ HW: EBAZ4205:: Цель данного туториала - повторить создание проекта Hello World с выводом текстовой строки в последовательный интерфейс UART, но на плате EBAZ4205. Для этого нужно будет учесть аппаратные особенности этой платы. Так же, отличием этого туториала является использование Vitis вместо более раннего варианта SDK.

ZYNQ HW: EBAZ4205:: Цель данного туториала - повторить создание проекта Hello World с выводом текстовой строки в последовательный интерфейс UART, но на плате EBAZ4205. Для этого нужно будет учесть аппаратные особенности этой платы. Так же, отличием этого туториала является использование Vitis вместо более раннего варианта SDK. ZYNQ HW: EBAZ4205: Часть 1 :: Цель данного туториала - повторить создание проекта Hello World с выводом текстовой строки в последовательный интерфейс UART, но на плате EBAZ4205. Для этого нужно будет учесть аппаратные особенности этой платы. Так же, отличием этого туториала является использование Vitis вместо более раннего варианта SDK.

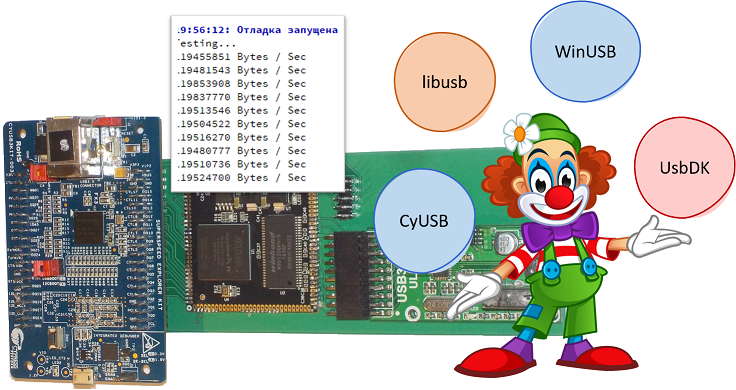

ZYNQ HW: EBAZ4205: Часть 1 :: Цель данного туториала - повторить создание проекта Hello World с выводом текстовой строки в последовательный интерфейс UART, но на плате EBAZ4205. Для этого нужно будет учесть аппаратные особенности этой платы. Так же, отличием этого туториала является использование Vitis вместо более раннего варианта SDK.  Боремся с таймаутами при использовании USB 3.0 через контроллер FX3, возникающими при определенных условиях :: Итак, в блоке из предыдущих трёх статей, мы рассмотрели, как можно изменить идеологию, принятую в первой версии комплекса Redd, заменив двухпроходную прокачку потоковых данных (сначала в буферное динамическое ОЗУ, а уже затем – в PC через интерфейс USB 2.0) на однопроходную (сразу в PC через интерфейс USB 3.0).

Боремся с таймаутами при использовании USB 3.0 через контроллер FX3, возникающими при определенных условиях :: Итак, в блоке из предыдущих трёх статей, мы рассмотрели, как можно изменить идеологию, принятую в первой версии комплекса Redd, заменив двухпроходную прокачку потоковых данных (сначала в буферное динамическое ОЗУ, а уже затем – в PC через интерфейс USB 2.0) на однопроходную (сразу в PC через интерфейс USB 3.0). Прокачиваем скрипты симуляции HDL с помощью Python и PyTest :: Все делают это. Ну ладно, не все, но большинство. Пишут скрипты, чтобы симулировать свои проекты на Verilog, SystemVerilog и VHDL. Однако, написание и поддержка таких скриптов часто бывает довольно непроста для типично используемых Bash/Makefile/Tcl.

Прокачиваем скрипты симуляции HDL с помощью Python и PyTest :: Все делают это. Ну ладно, не все, но большинство. Пишут скрипты, чтобы симулировать свои проекты на Verilog, SystemVerilog и VHDL. Однако, написание и поддержка таких скриптов часто бывает довольно непроста для типично используемых Bash/Makefile/Tcl. Учимся работать с USB-устройством и испытываем систему, сделанную на базе контроллера FX3 :: В двух предыдущих статьях мы сделали USB 3.0 систему на базе контроллера FX3. Пришла пора научиться работать с нею из своих программ для PC. Ну, и попутно понять, насколько получившаяся система пригодна для практического применения

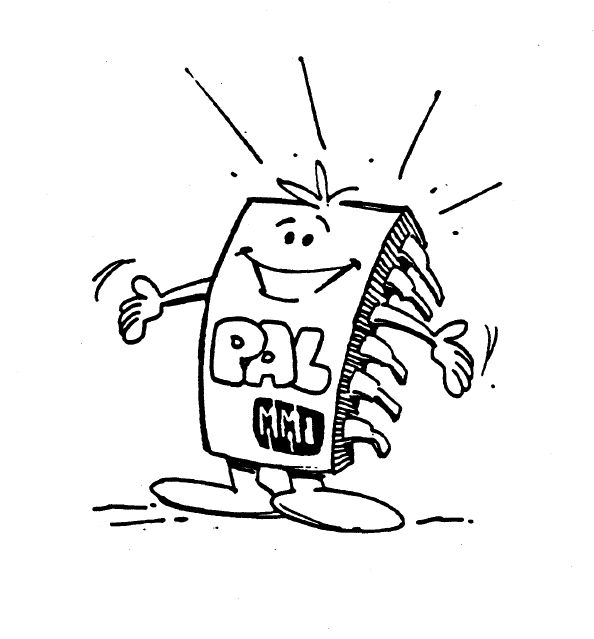

Учимся работать с USB-устройством и испытываем систему, сделанную на базе контроллера FX3 :: В двух предыдущих статьях мы сделали USB 3.0 систему на базе контроллера FX3. Пришла пора научиться работать с нею из своих программ для PC. Ну, и попутно понять, насколько получившаяся система пригодна для практического применения PAL, GAL и путешествие в цифровое ретро :: Обзор того, что «выстрелило» и стало мэйнстримом.

PAL, GAL и путешествие в цифровое ретро :: Обзор того, что «выстрелило» и стало мэйнстримом.

Стримы

ПЛИС и АЦП :: 1000 и 1 способ реализации SPI :: Часть 1

ECO Flow - извращенное проектирование на FPGA

Gate Level FPGA :: основы проектирования цифровых устройств

ПЛИСамоделки :: Работа с Видео на FPGA:: Колаб :: часть 1

ПЛИС и АЦП :: 1000 и 1 способ реализации SPI :: Часть 2

Вакансии

Kraftway :: FPGA разработчик. Полная занятость (Москва)

Kraftway :: FPGA разработчик. Полная занятость (Москва) Начинающий FPGA/ПЛИС разработчик (Раменское, Жуковский, Бронницы)

ООО «СКБ «Радиотехпроект» :: FPGA-разработчик - FPGA Design Engineer

ООО «СКБ «Радиотехпроект» :: FPGA-разработчик - FPGA Design Engineer

Есть чем поделиться для следующего дайджеста? Напишите в личку.