Выпущен новый релиз симулятора ПЛИС Active-HDL 12.0!

Компания ALDEC выпустила новый релиз симулятора ПЛИС Active-HDL 12.0! Active-HDL 12.0 позволяет разработчикам ПЛИС в полной мере использовать многие функции последней версии VHDL и помогает повысить эффективность проверки проекта.

Последний релиз поддерживает новые функции языка VHDL-2019 (IEEE 1076-2019), что упрощает язык, снимает определенные ограничения, которые присутствовали в более ранних версиях, и вводит новые интерфейсы прикладного программирования (API).

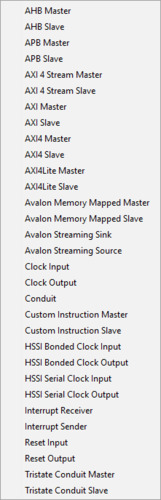

В OSVVM 2020.08 были добавлены усовершенствования, дающие пользователям доступ к новым возможностям отслеживания требований, обновленным сценариям, компонентам полной проверки AXI4 и независимым от модели транзакциям, на основе бесплатных методологий с открытым кодом.

В последней версии Active-HDL также представлены улучшения языка SystemVerilog, которые включают начальную поддержку многомерных массивов экземпляров, предварительную поддержку неразрешенных определяемых пользователем типов цепей и предварительную поддержку уникальных ограничений. Также доступны несколько нестандартных расширений для SystemVerilog. К ним относятся разрешение на управление выходными данными переменного типа для блоков синхронизации посредством непрерывного присвоения, разрешение использования циклов foreach для элементов подмассива, и назначение виртуального интерфейса с modport для виртуального интерфейса без modport.

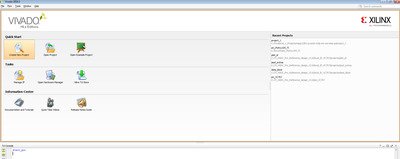

Active-HDL - это интегрированная универсальная среда проектирования (IDE), которая пригодна для работы с ПЛИС всех ведущих вендоров, и включает в себя полный набор инструментов графического проектирования и работы с HDL-кодом, а также симулятор RTL/gate-level для быстрой разработки и верификации FPGA. Эти функции в сочетании с поддержкой последних версий языка VHDL позволяют инженерам создавать, поддерживать, повторно использовать и легко проверять свои проекты.

«Язык VHDL-2019 был запрошен пользователями, ранжирован пользователями, изучен пользователями, написан пользователями и проголосован сообществом VHDL», - комментирует Джим Льюис, директор по обучению VHDL в SynthWorks и председатель рабочей группы IEEE 1076 VHDL. «Как и в случае с VHDL-2008, компания Aldec находится в авангарде внедрения новых языковых функций. Это хорошая новость, поскольку сообщество готово начать использовать VHDL-2019».

Для ознакомления с продуктом доступна бесплатная студенческая "lite" версия Active-HDL