Новые возможности симулятора Active-HDL 12

В новой версии симулятора ПЛИС Active-HDL v12, которая вышла в 2021 г., представлены следующие улучшения:

Улучшения в симуляции Verilog / SystemVerilog

- Многоразмерные массивы экземпляров

- Неразрешимые пользовательские типы цепей

- Уникальные констрейны (ограничения)

- Передача элемента массива как аргумента в метод mailbox

- Нестандартные расширения к языку:

- Переменные типы выходов блоков тактирования могут управляться непрерывным назначением.

- Циклы foreach могут итерировать по элементам подмассива

- Назначение виртуального интерфейса modport интерфейсу без modport

- Ассерции SystemVerilog могут быть использованы в PSL vunit.

Улучшения в симуляции VHDL-2019

- Параметры, передаваемые в защищенные методы, могут иметь тип "файл", "доступ", или композитный тип.

- Параметры функции могут иметь тип "доступ" или "защищенный".

- Общая переменная типа "защищенный" может быть объявлена как формальная переменная "порт".

- Дженерики могут быть отображены в вызове подпрограммы, позволяя пропустить инстанциацию подпрограммы.

Улучшения производительности

- Изменение и улучшение управления памятью, и проверка и отчет о проблемах занятия памяти в процессе симуляции.

- Улучшение производительности процесса элаборации для крупных проектов, скомпилированных в режиме отладки, и содержащих много констант, параметров или параметризованных типов.

- Улучшение решателя случайных констрейнов

Поддержка новых версий программных продуктов других вендоров по мере появления:

- Synopsys SynplicitySynplifyPro

- Xilinx Vivado202x.x

- MicrosemiLibero

- Intel QuartusPrime Standard / Pro

- Lattice Radiant Software LSE 2.x

Поставка предварительно скомпилированных библиотек вендоров:

- Intel®Quartus® Prime Standard / Pro

- Lattice® Diamond

- Lattice® Radiant

- Xilinx®Vivado

- MicrosemiLibero®SoC

- OSVVM

- UVVM

Улучшения в редакторе машины состояний

- Отдельное хранение настроек Code Generation Settings для каждого файла диаграмм состояний

- Набор настроек в диалоговом окне зависит от выбранного языка HDL

- Улучшение генерации кода, особенно полезное при использовании ALINT-PRO для проверки качества кода

Окно стимулов

- Новый интерфейс для более удобного создания виртуальных источников сигнала

- Окно создания стимулов сделано независимым от других инструментов Active-HDL

- Возможность добавлять созданные стимулы к сигналам, представленным в окне просмотра диаграмм

- Возможность экспортировать созданные стимулы в файлы XML и DO, или импортировать

Другие улучшения

- Поддержка локальных переменных типа real в ассерциях

- Поддержка типа векторов sc_bv шириной более 32 бит

- В отчете о покрытии - различие между оператором if без else и оператора if, имеющего else

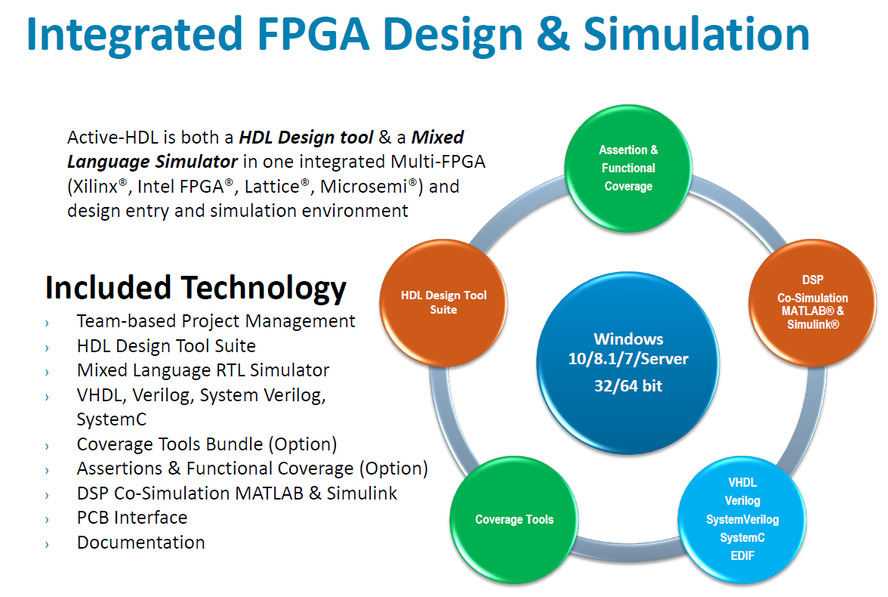

В целом инструмент Active-HDL стал еще более удобным в работе и мощным. Возможность использовать универсальный симулятор для работы с проектами HDL для любых ПЛИС ведущих вендоров, быстрая компиляция проекта, удобный и эффективный симулятор делают Active-HDL весьма полезным инструментом для разработчиков сложных проектов ПЛИС, позволяющим повысить эффективность и производительность разработки.