Модельное проектирование ПЛИС и ASIC в контексте функциональной безопасности

Помимо ASIC, FPGA и SoC играют все большую роль во все большем числе систем и приложений благодаря своим уникальным свойствам: гибкости, высокой пропускной способности, низкой задержке и производительности на ватт.

Ключевым фактором успеха междисциплинарных проектов на FPGA, SoC и ASIC является эффективная коммуникация и сотрудничество между командами, а также ранняя валидация и верификация проекта. Быстрое реагирование на меняющиеся требования в динамичных бизнес-средах, таких как автономные и роботизированные системы, является значительным конкурентным преимуществом. Требования функциональной безопасности создают дополнительную проблему в автомобильной, медицинской, железнодорожной и других отраслях промышленности.

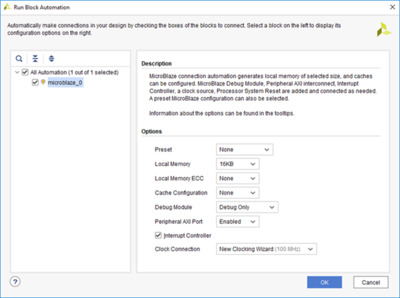

На этом вебинаре мы обсудим интегрированный рабочий процесс разработки и реализации алгоритмов обработки сигналов, управления и видения на ПЛИС, ASIC и SoC при решении вышеперечисленных задач. Мы кратко рассмотрим процесс от разработки требований до архитектурного моделирования, перейдем к моделированию для реализации, а затем к генерации HDL-кода с верификацией и валидацией на каждом этапе. Мы покажем, как интегрированная цепочка инструментов проектирования на основе моделей помогает вам оптимизировать соблюдение функциональных стандартов безопасности, таких как ISO 26262, IEC 61508 или IEC 62304

Вебинар состоится 22 января 2021 в 12:00 Мск