О важности временных ограничений при проектировании ПЛИС

“The LEC2 Workbench” запускает серию заметок в блоге Lattice Semiconductor, посвященных разработке приложений с использованием продуктов Lattice. Эти посты написаны экспертами по проектированию ПЛИС из Центра компетенций Lattice Education (LEC2), полной учебной и образовательной программы, разработанной в тесном сотрудничестве с Lattice Semiconductor. Программа обучения будет включать в себя весь портфель Lattice: ПЛИС и стеков решений, включая инструменты и методы проектирования.

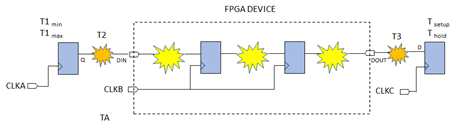

В первой заметке рассматриваются базовые понятия и временные ограничения