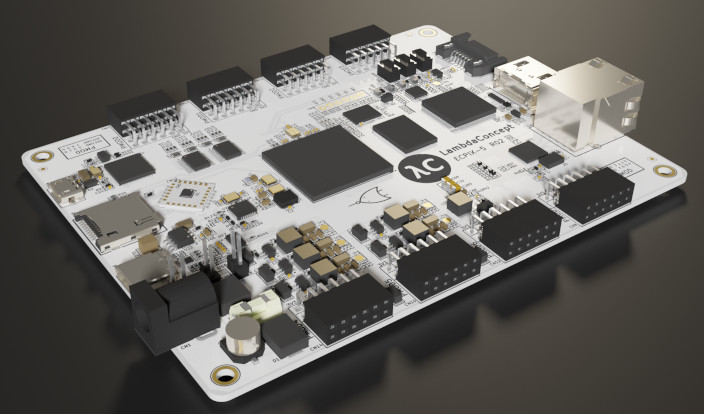

Silice - open source язык для FPGA

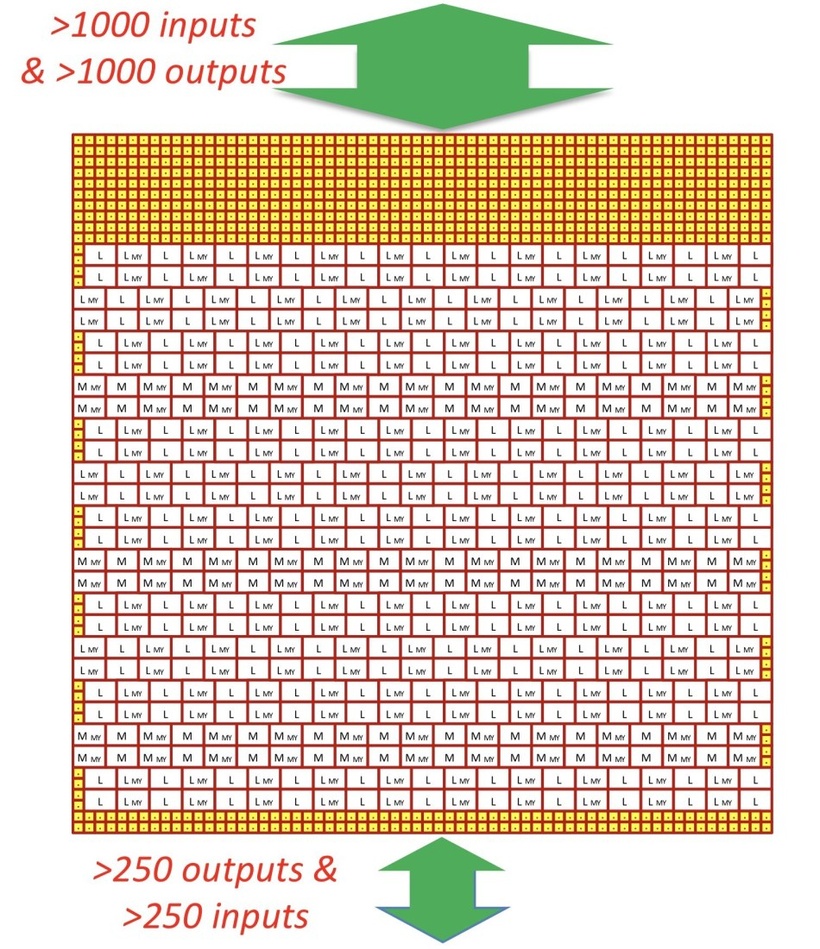

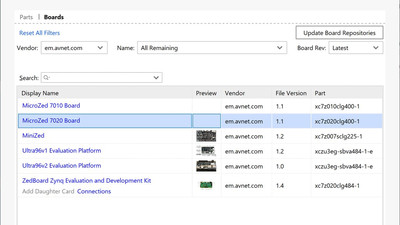

Silice упрощает создание прототипов и реализацию алгоритмов на ПЛИС. Он обеспечивает удобную, но тонкую абстракцию над Verilog, упрощая разработку при этом не теряя контроля над аппаратной частью. Он обладает возможностью группировки сигналов, определения общих интерфейсов и схем, создания экземпляров блочной памяти, описания конвееров, работы с несколькими тактовыми доменами и автоматического управления триггерами. Он даёт возможность описывать части вашего проекта в виде последовательностей операций, подпрограмм, которые можно вызывать, и использовать операторы, такие как while и break, описывающие операции и алгоритмы, которые выполняются параллельно и точно синхронизированы. Silice обнаруживает комбинаторные циклы и многие другие случаи, подверженные ошибкам, и оснащен Lua-препроцессором, обеспечивающим расширенную генерацию кода.

Silice не является языком высокоуровнего синтеза: он остается близким к железу и позволяет в полной мере использовать архитектуры FPGA с точным контролем того, как ваш проект соотносится с имеющимися аппаратными ресурсами. Вы по - прежнему контролируете то, что происходит на каждом такте, с предсказуемыми правилами управления.

Подробнее смотрите на странице проекта Silice