Заметка: Решения Exostiv позволяют глубже понять что происходит внутри FPGA

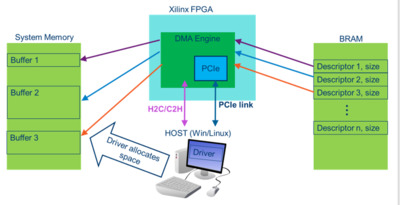

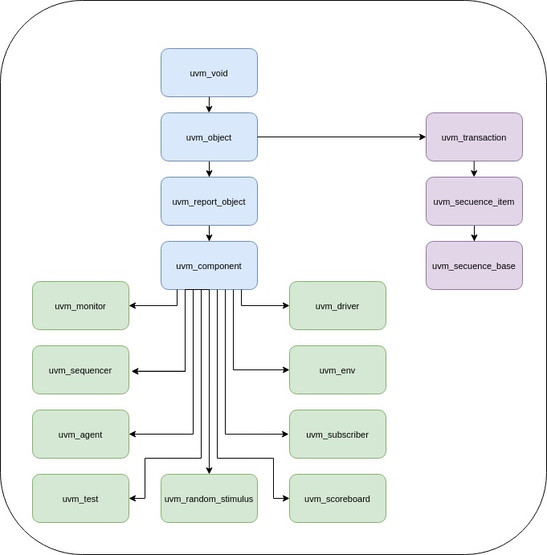

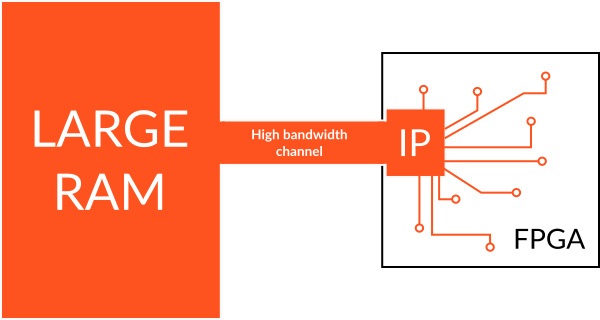

В заметке описан подход записи данных во внешнюю память и основное отличие этого подхода от снятия данных через JTAG, рассмотрена запись событий с разделением по времени, показаны основные преимущества такого подхода при отладке проектов.

В скором времени состоится вебинар, на котором Вы сможете узнать все подробности работы Exostiv

Подробнее читайте на сайте компании.

This note describes the approach of writing data to external memory and the main difference between this approach and taking data via JTAG.it also discusses the recording of events with time division, and shows the main advantages of this approach when debugging projects.

A webinar will be held soon, where you can learn all the details of Exostiv's product

Read more on the company's website.