Основы AXI часть 7 - Подключение к PS с помощью AXI4-Lite и Vitis HLS

Вступление:

В "Основы AXI часть 6 – Введение в AXI4-Lite в Vitis HLS" мы узнали, как создать IP в HLS с интерфейсом AXI4-Lite с использованием кода на C.

В этом блоге мы узнаем, как экспортировать наше IP, чтобы использовать его в Vivado Design Suite, как подключить его к другим IP ядрам и процессору и как запустить наш проект на плате.

В этом уроке 3 раздела:

1. Экспорт нашего IP из Vitis HLS.

2. Создайте оборудование с помощью Vivado Design Suite.

3. Написание ПО в среде Vitis и запуск его на плате.

1. Экспорт нашего IP:

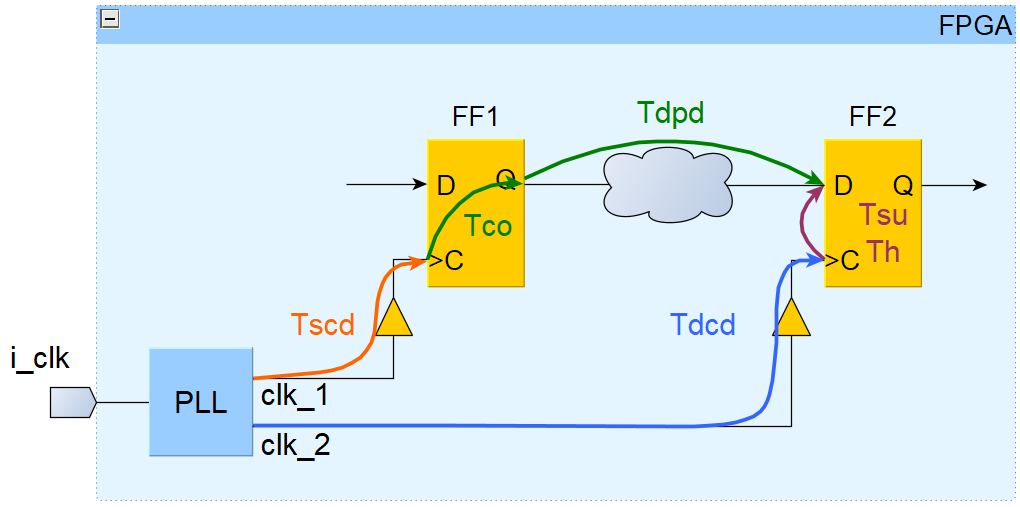

В "Основы AXI часть 6 – Введение в AXI4-Lite в Vitis HLS" было создано IP ядро,котрое используюет протокол AXI4-Lite. Если мы хотим подключить наше IP к любому другому IP или к PS, то сначала нужно синтезировать программный код в RTL. Затем экспортировать наш RTL IP в Vivado Design Suite, где он быдет подключен к другим IP ядрам или к PS.

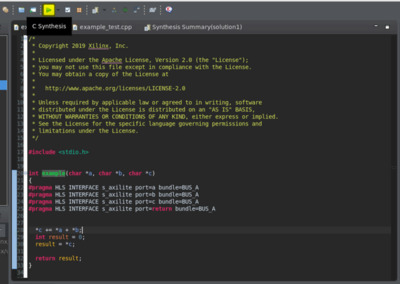

1.1 Отредактируйте код, как показано ниже, и сохраните его.

int example(char *a, char *b, char *c)

{

#pragma HLS INTERFACE s_axilite port=a bundle=BUS_A

#pragma HLS INTERFACE s_axilite port=b bundle=BUS_A

#pragma HLS INTERFACE s_axilite port=c bundle=BUS_A

#pragma HLS INTERFACE s_axilite port=return bundle=BUS_A

*c += *a + *b;

int result = 0;

result = *c;

return result;

}

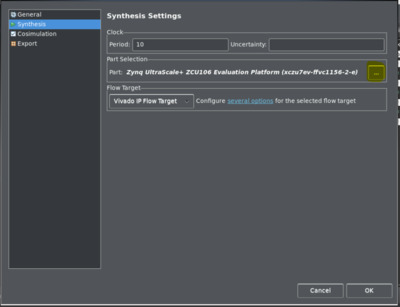

1.2. Поскольку этот код будет запускаться на плате, то нужно будет изменить настройки синтеза, чтобы они соответствовали нашей плате.

В данном случае используется Zynq UltraScale + ZCU106. Чтобы изменить целевое устройсво, нужно перейти в Solution -> Solution Settings -> Synthesis Settings, затем, чтобы определить новое устройство,

выберите значек троеточия (подсвеченно на картинки ниже).

1.3. Запустите синтез кода, нажав зеленую кнопку (значек play) "png" в верхней части экрана. Это превратит наш код в RTL:

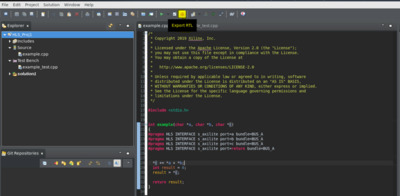

1.4. После завершения синтеза можно будет экспортировать RTL, нажав кнопку Export RTL на панели инструментов "png" или щелкнув Solution -> Export RTL, чтобы открыть диалоговое окно «Экспорт RTL».

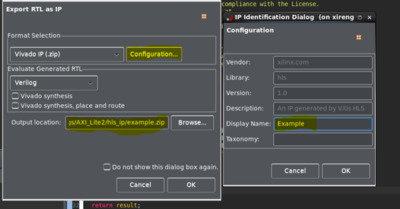

1.5. Диалоговое окно должно открыться, как показано на снимке экрана ниже.

Здесь можно ознакомиться подробное с описанием всех доступных опций диалогового окна.

*Выберите опцию configuration, чтобы уточнить устройство для создания RTL IP. Измените отображаемое имя на Example и выберите ОК. Когда вы откроете своё IP в Vivado Design Suite появится новое имя.

*Нажмите кнопку Browse, чтобы выбрать расположение и имя для выводимого файла Vivado IP (.zip). Полученный ZIP-файл будет содержать ваш RTL IP, который можно импортировать в Vivado Design Suite.

1.6. Подождите, пока незакончится экспорт, затем откройте Vivado Design Suite и выберите вариант создания нового проекта:

1.7. Выберите Next. При выборе устройсва важно выбрать то же, которое вы выбрали в Vitis HLS при создании проекта. Если вы не уверены, выбранное устройство можно найти в solution settings -> synthesis settings в Vitis HLS. Если вы не выберете тот же девайс, у вас могут возникнуть проблемы с импортом вашего IP в Vivado Design Suite.

Наконец, выберите Finish, чтобы открыть пустой проект.

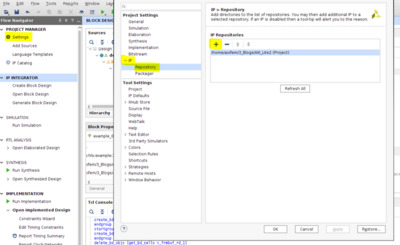

1.8. Чтобы использовать сгенерированный IP в проекте Vivado, мы сначала должны добавить ваш новый IP репозиторий в проект Vivado. Это папка, в которой находится экспортированный файл .zip из Vitis HLS. Для этого выберите

Settings -> IP -> Repository. Нажмите кнопку + и выберите место, куда вы экспортировали своё IP в Vitis HLS (смотри пункт 1.6).

Выберите Apply в нижней части диалогового окна, затем нажмите ОК.

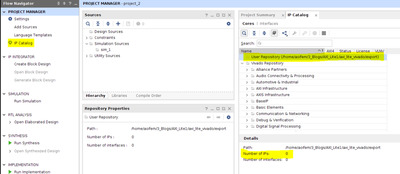

1.9. Выберите IP Catalog. Теперь вы должны увидеть свой новый репозиторий в каталоге.

Если IP был импортирован успешно, количество IP ядер, перечисленных в окне сведений, теперь должно быть 1.

ПРИМЕЧАНИЕ. Если в списке 0 IP ядер, вы можете щелкнуть правой кнопкой мыши на новый репозиторий и выбрать Add IP to Repository. Выберите ZIP-файл, который вы экспортировали из Vitis HLS. После этого вы должны увидеть количество IP ядер в этом репозитории как 1. Если нет, дважды проверьте, что плата, которую вы выбрали в Vitis HLS, совпадает с той, которую вы используете в Vivado, иначе ваше IP может быть несовместимым.

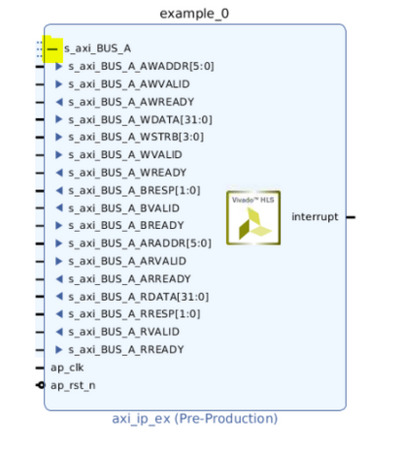

1.10. В Flow Navigator выберите Create Block Diagram.

В открывшейся вкладке нажмите кнопку + и найдите имя, которое вы дали своему IP, в Vitis HLS (смотри пункт 1.5, в данном случае Example).

Поздравляю! Вы успешно создали IP, экспортировали его из Vitis HLS и добавили на блок-схему в Vivado Design Suite.

При нажатии кнопки + рядом с s_axi_BUS_A отображается диапазон различных портов. Дополнительную информацию об этом можно найти в (PG155) в разделе Port Descriptions.

Подключение к PS:

2. Создайте своё устройство:

Возможно, вы захотите подключиться к PS, чтобы воспользоваться его функциями. Добавление PS IP, такого как Zynq UltraScale + MPSoC IP(доступный на плате ZCU106), позволяет вам это сделать.

Более подробную информацию о Zynq UltraScale + MPSoC IP можно найти здесь.

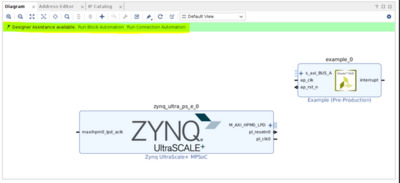

2.1. Добавьте IP Zynq UltraScale + MPSoC на свою блок-схему. После добавления в верхней части экрана выберите Run Connection Automation.

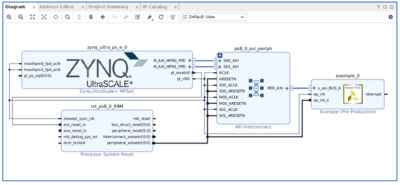

2.2. У вас должна получиться диаграмма изображенная ниже. Кроме того, вы можете добавить все элементы для PS IP вручную и подключить их самостоятельно. У вас должна получиться диаграмма которая показана ниже:

Создайте HDL оболочку, щелкнув правой кнопкой мыши <design_name>.bd на вкладке Sources. Запустите синтез, затем имплементацию и сгенерируйте bitstream. Затем выберите File -> Export -> Export Hardware. Обязательно выберите параметр для подключения bitstream и обратите внимание на выбранное место экспорта. В результате будет создан файл XSA, содержащий всю информацию об устройстве. Теперь вы можете закрыть Vivado.

3. Написание программного обеспечения

Теперь, когда ваше оборудование создано и экспортировано, нам нужно написать программное обеспечение, которое сообщает нашему оборудованию, что делать. Мы будем писать наше ПО в среде разработки Vitis. Вам нужно будет загрузить Vitis Core Development Kit с сайта Xilinx.

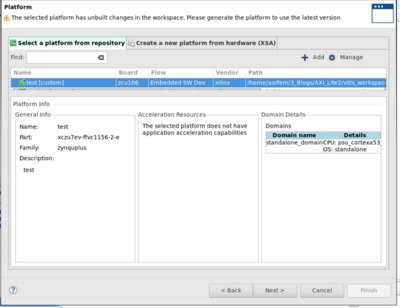

3.1. Откройте Vitis. В открывшемся меню выберите Create Platform Project. Это будет основой нашего проекта, и мы добавим сюда информацию об устройстве (файл XSA), а также напишем программного обеспечения. При появлении запроса выберите вариант create from XSA file. Затем нам нужно выбрать местоположение экспортированного файла XSA (смтри раздел 2.3). Продолжите пока проетк настроется и нажмите Finish.

3.2. Далее нам нужно создать проект программы. Он будет основан на нашем проекте ПЛИС и необходим для запуска приложения на нашей целевой плате. Выберите File -> New -> New Application Project.

3.3. При появлении запроса выберите вариант Select a platform from a repository. Выберите проект ПЛИС, созданный на шаге 3.1, затем нажмите Next.

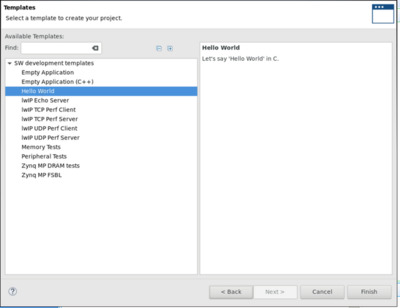

3.4. Выберите шаблон Hello World и нажмите Finish.

3.5. Код Hello World теперь можно увидеть в разделе <application_project_name> /src/helloworld.c. В качестве проверки работоспособности мы собираемся загрузить пример на нашу плату через JTAG и вывести сообщение Hello World с помощью UART.

Для этого подключите целевую плату и откройте программное обеспечение эмулятора терминала, например Tera Term, чтобы прочитать выходные сообщения. Если вы не знаете, как это сделать, обратитесь к руководству пользователя вашей платы. Скомпилируйте и запустите программу. Если все сделано правильно, вы должны увидеть сообщение Hello World в Tera Term.

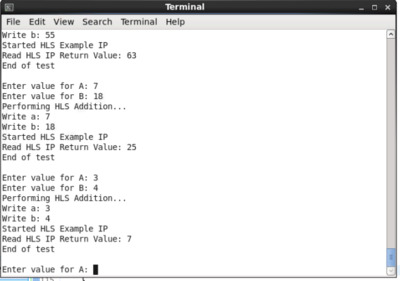

3.6. Теперь, когда мы знаем, что наша плата подключена правильно, давайте напишем код, который использует наш HLS IP. Скопируйте код из Vitis_Code.c (прилагается к этому руководству, можно скочать по ссылке на оригинальную статью) и вставьте его в helloworld.c, заменив исходный код helloworld.

Сохраните, соберите и снова запустите программное обеспечение. На этот раз в Tera Term вам будет предложено ввести два входа, A и B. Это будут входы для вашего HLS IP, которые будут добавлены вместе и отобразится результат.

Примечание. Поскольку A и B были определены в Vitis HLS как тип char, следует вводить только значения до 127.

В примере кода используются функции, которые автоматически создаются средой Vitis, что делает разработку очень быстрой и простой.

Используемые функции можно найти в файле с именем X<HLS_IP_name>.h и в <platform_project>/hw /drivers/<ex_name>/src. Функции подробно описаны здесь. Взгляните на этот файл и другие связанные файлы в этой папке. Их можно редактировать для дальнейшего управления вашим IP, программирования прерывания и т.д.