FPGA Daily News #033

Short FPGA News collection for 03-Mar-2022

#NoWarPlease

- Workshop: Introduction to oneAPI and to Intel® DevCloud

- Inavate AV | av link releases multiwindow video processor fa

AV Link has released a multi-window video processor family featuring Xilinx Kintex UltraScale device

- EETimes - eFPGA LUTs Will Outship FPGA LUTs Later This Decade

FPGA used to be a "poor man's ASIC," but today FPGA technology is strategically important for cloud data centers and communications systems

- Global Field Programmable Gate Array (FPGA) in Cyber Security Industry Market Size | By Type | By Application

Get Field Programmable Gate Array (FPGA) in Cyber Security Industry market research report, manufacturers, data forecasts and consulting services by approaching Credence Research Reports.

- Better Application and Cloud Performance with Vcinity (Brief)

Read how to improve app and cloud performance with better data infrastructure via access to data from anywhere, in real time, with Vcinity and Intel.

- 5G cascaded channel estimation using convolutional neural networks - ScienceDirect

Cascaded channels have been considered in several physical multipath propagation scenarios. However they are subject to phenomena such as multipath sc…

- How to Easily Migrate From Xilinx® Spartan®-6 Devices to Microchip FPGAs

Wednesday, February 23, 2022 at 08:00 AM Pacific Standard Time.

- Fostering a Chiplet Ecosystem for the Future of Moore’s Law

The next step is an open chiplet ecosystem and ubiquitous interconnect at the package level.

- Versal Card Streamlines ACAP FPGA AI Development | Electronic Design

Xilinx's VCK5000 Versal Development Card for AI inference leverages the company's Vitis software.

- Open-Source IC Design Tools Workshop – OSFPGA

Open Source IC Design Tools Workshop 4-day workshop on Analog and Digital IC design flow using Open

- AmpliTech Group & SN2N Develops an Innovative FPGA Solution with High Levels of Encryption

- Top Applications of FPGAs

FPGAs have revolutionized digital circuit design and embedded systems circuit design with programmable architecture and high density. Applications for FPGAs include...

- Nvidia says its ‘proprietary information’ is being leaked by hackers - The Verge

Supposed hackers demand removal of cryptomining limits

- UVVM - Bringing UVM to VHDL | LinkedIn

- Improving Soft Error Reliability of FPGA-based Deep Neural Networks with Reduced Approximate TMR | IEEE Conference Publication | IEEE Xplore

Deep Neural Networks (DNN) are recently used in different fields such as autonomous driving, cancer detection, and also space explorations. A certain level of reliability of DNN are indeed needed to be applied in these fields. More recently, FPGA devices have become a target platform for DNN applications due to their high flexibility and computational power. Unfortunately, the SRAM-based FPGAs are considered to be susceptible to soft errors which can lead to errors in execution. Triple Modular Redundancy (TMR) is one of the effective mitigation techniques for masking SEUs for FPGA but causes an increase in power consumption and area overhead. In this study, we evaluate the reliability of MNIST DNN implemented in Xilinx SRAM-based FPGA. Through fault injection simulation, we identified the most vulnerable parts of the design that SEU can generate errors. We improved the SEU reliability of DNN with our proposed hardening strategy named reduced approximate TMR. SEU reliability was enhanced by applying reduced approximate TMR to the most sensitive layers of MNIST DNN, achieving 40% improvement in reliability while recourses utilization and power consumption were increased by 8% and 4%, respectively.

- What is ASIC - FPGA - SoC? | Explanation, Differences & Applications - YouTube

- Xiphera's white paper addresses security on open fronthaul | Xiphera

Xiphera's MACsec IP cores secure also synchronisation messages.

- F Light: FPGA Acceleration of Lightweight DNN Model Inference in Industrial Analytics | SpringerLink

Deep Neural Networks (DNNs) have been recently in the focus of interest owing to their high-quality results in various application domains of big data analytics. The lack of end-to-end toolchains...

- MicroZed Chronicles: Partial Configuration Introduction

Getting the most efficient utilization of our FPGA does not mean that we need to have the logic resources dedicated to all use cases. We could, for example, have several different FPGA designs which are loaded in as required with one FPGA implementing several different functionalities. This could be the case in image processing or signal processing pipelines for example. Often when we examine the contents of these FPGA designs, however, only a small element of the FPGA design is different. Take

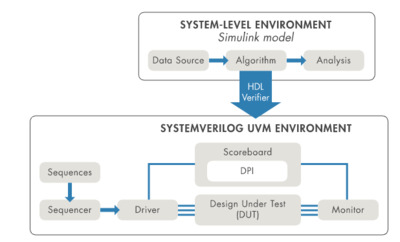

- SystemUVM™ — Empowering UVM Engineering - Breker Verification Systems

SystemUVM is a class library built on top of PSS that makes it almost indistinguishable from UVM with SystemVerilog.