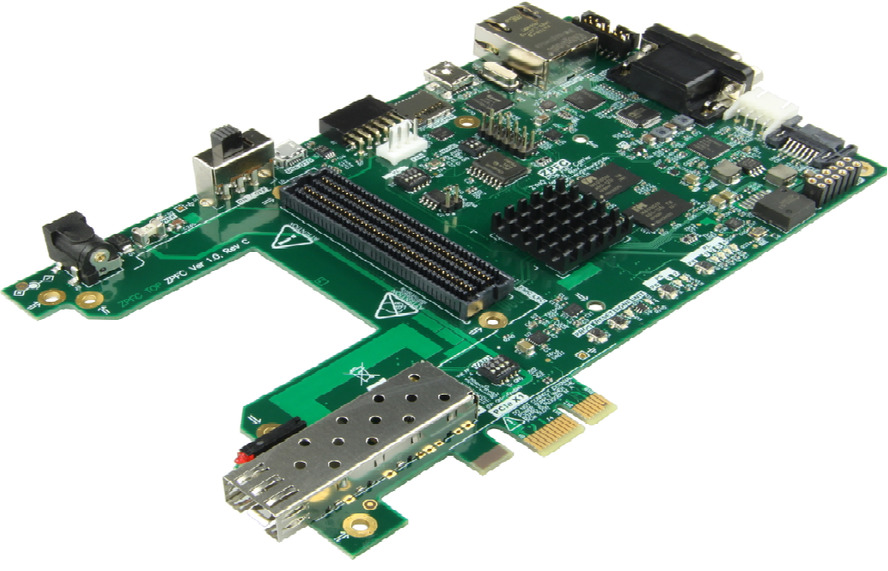

Релиз: Zynq PCIe FMC отладка на Zynq-7000 XC7Z015 SoC от Trenz

На плате установлены все необходимые компоненты, требуемые для встроенных систем, включая DDR3 память, 1x PCI Express, GigaBit Ethernet PHY, I/O общего назначения, USB-UART

Ключевые особенности:

- Zynq-7000 XC7Z015-1FFG485C AP SoC

- 1 GB DDR3 memory (two [512 Mb x 16] devices) on the processing system (PS) side

- 256 Mb Quad-SPI flash memory

- USB 2.0 ULPI (UTMI+ low pin interface) transceiver with micro-B USB connector

- Secure Digital (SD) connector

- Clock sources:

- Fixed 125 MHz LVDS oscillator (differential)

- Fixed 33.33 MHz LVCMOS oscillator connected to PS (single-ended)

- Fixed 100.00 MHz LVCMOS oscillator connected to PL (single-ended)

- GTP transceivers:

- FMC LPC connector (one GTX transceiver)

- PCI Express (1x lanes)

- Small form-factor pluggable (SFP) connector

- SATA Connector

- PCI Express endpoint connectivity, Gen1 1-lane (x1)

- SFP Connector

- Ethernet PHY RGMII interface with RJ-45 connector

- USB-to-UART bridge with mini-B USB connector

- VGA codec with VGA connector

- I2C bus

- M24C08 EEPROM (1 kB)

- FMC LPC connector

- Quad SPI Flash memory

- Platform cable header JTAG configuration port

- 20-pin TRENZ JTAG header

- Dual 12-bit 1 MSPS XADC analog-to-digital front end

- Status LEDs:

- Ethernet status

- Power

- 12V Input Power On

- FPGA INIT

- FPGA DONE

- User I/O:

- Four (PL) user LEDs

- One (PL) user pushbutton

- One (PL) user DIP switch (4-pole)

- Two Dual row Pmod GPIO headers

- AP SoC PS Reset Pushbuttons:

- SRST_B PS reset button

- POR_B PS reset button

- VITA 57.1 FMC LPC connector

- Power on/off slide switch

Скачать документацию и узнать подробности можно на странице релиза

It provides features common to many embedded processing systems, including DDR3 component memory, one-lane PCI Express interface, GigaBit Ethernet PHY, general purpose I/O, and one USB-UART interface. Other features can be supported using VITA-57 FPGA mezzanine card (FMC) attached to the low pin count (LPC) FMC connectors.

Key Features

- Zynq-7000 XC7Z015-1FFG485C AP SoC

- 1 GB DDR3 memory (two [512 Mb x 16] devices) on the processing system (PS) side

- 256 Mb Quad-SPI flash memory

- USB 2.0 ULPI (UTMI+ low pin interface) transceiver with micro-B USB connector

- Secure Digital (SD) connector

- Clock sources:

- Fixed 125 MHz LVDS oscillator (differential)

- Fixed 33.33 MHz LVCMOS oscillator connected to PS (single-ended)

- Fixed 100.00 MHz LVCMOS oscillator connected to PL (single-ended)

- GTP transceivers:

- FMC LPC connector (one GTX transceiver)

- PCI Express (1x lanes)

- Small form-factor pluggable (SFP) connector

- SATA Connector

- PCI Express endpoint connectivity, Gen1 1-lane (x1)

- SFP Connector

- Ethernet PHY RGMII interface with RJ-45 connector

- USB-to-UART bridge with mini-B USB connector

- VGA codec with VGA connector

- I2C bus

- M24C08 EEPROM (1 kB)

- FMC LPC connector

- Quad SPI Flash memory

- Platform cable header JTAG configuration port

- 20-pin TRENZ JTAG header

- Dual 12-bit 1 MSPS XADC analog-to-digital front end

- Status LEDs:

- Ethernet status

- Power

- 12V Input Power On

- FPGA INIT

- FPGA DONE

- User I/O:

- Four (PL) user LEDs

- One (PL) user pushbutton

- One (PL) user DIP switch (4-pole)

- Two Dual row Pmod GPIO headers

- AP SoC PS Reset Pushbuttons:

- SRST_B PS reset button

- POR_B PS reset button

- VITA 57.1 FMC LPC connector

- Power on/off slide switch

Read More