Сколковская школа синтеза цифровых схем на Verilog

Уважаемые участники сообщества FPGA разработчиков FPGA-Systems.ru Как Вы знаете, одной из целей нашей деятельности является популяризация направления разработок на FPGA/ПЛИС среди начинающих разработчиков и инженеров. А так же практически все из нас знают или слышали про Юрия Панчула. Юрий в очередной раз проводит школу-семинар по проектированию цифровых микросхем и поэтому прошу Вас максимально распространить это приглашение на мероприятие. С уважением, команда проекта FPGA-Systems.ru

Организатор выставки ChipEXPO - 2020 (15 - 17 сентября 2020 года, Инновационный Центр «Сколково»,Технопарк) приглашает студентов младших курсов и старших школьников познакомится с тремя технологиями, которые сделали возможным наш мир смартфонов, быстрого интернета и беспилотных автомобилей.

Они возникли еще в 1980-х, повысили производительность труда инженеров на два порядка, и также позволили создавать прототипы чипов без изготовления их на фабрике.

Эти технологии сейчас используют все: как американские Apple, NVidia,Tesla, так и российские компании ЭЛВИС и НИИСИ, которые проектируют процессоры для космических кораблей

и камер для распознавания лиц.

Технологии цифрового синтеза позволяют создавать очень сложные устройства, но базовые принципы их вполне доступны для продвинутого школьника.

Из-за короновируса семинар будет проводится в режиме онлайн, в рамках деловой программы выставки ChipEXPO-online, поэтому принять участие в нем смогут не только школьники Москвы, но и школьники всей России, Украины, Казахстана, Калифорнии и других стран и регионов.

Историческая справка:

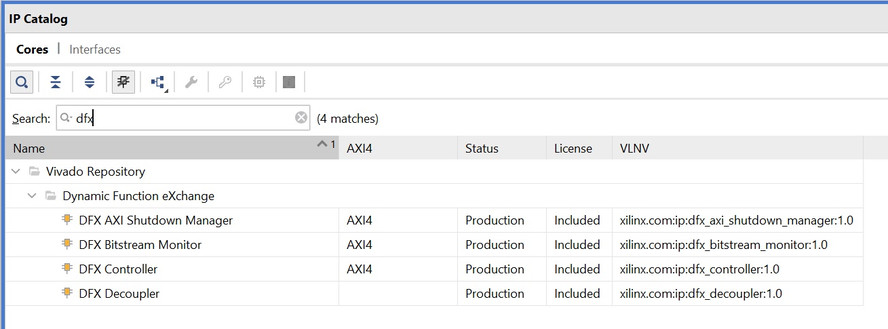

Verilog HDL (Hardware Description Language) - это язык текстового описания аппаратуры. Он используется для проектирования, моделирования, верификации цифровых микросхем, плат и систем.

Язык Verilog был разработан в 1984-1985 году Филом Морби (Phil Moorby) во время его работы в компании Gateway Design Automation. Тогда же появился первый Верилог симулятор: Verilog-XL. Позже компанию Gateway купила Cadence Design Systems и в 1990-м сделала Verilog HDL публичным достоянием. В 1995-м году язык стал стандартом IEEE-1364-1995, IEEE Standard Hardware Description Language Based on the Verilog(R) Hardware Description Language.

Позднее появилась "расширенная" версия языка - это SystemVerilog, разрабатываемый

Accellera (www.accellera.org).

В SystemVerilog упор сделан на верификацию проектов, язык содержит элементы

объектно-ориентированного программирования.

Как научиться проектировать, моделировать и верифицировать схемы на Verilog?

Главная проблема изучения этого языка для людей, которые уже умеют программировать: Verilog требует другой ментальной модели вычислений. Не цепочки инструкций, как в классических языках программирования, а параллельно работающие облака комбинационной логики, которые хранят состояния в регистрах последовательностной логики.Чем раньше мозг подсаживается на Verilog - тем лучше. Это как с игрой на скрипке или профессиональным спортом - виртуозы и олимпийские чемпионы занимаются этим с детства.

Но как сделать Verilog интересным для школьника? Простые упражнения с мигающими огоньками на платах ПЛИС/FPGA быстро надоедают, упражнения посложнее, типа конструирования процессоров, требуют слишком многих вложений внимания перед тем, как стать интересными.

Упражнения с сенсорами типа датчика освещения сводятся к конструированию конечного автомата для протоколов SPI или I2C на ПЛИС и не показывают все аспекты проектирования схем.

После трех лет экспериментирования со школьниками в Москве, Киеве и Новосибирске был найден

универсальный способ для быстрого и интересного введения школьника в Verilog с помощью проектирования видеоигр в железе. На этом примере лучше всего усваиваются концепции параллельности, модульной иерархии, проектирования небольшого конвейерного тракта данных и написания конечного автомата для сценария игры.

Базовый вариант можно гибко менять, создавая новые игры.

Автором и энтузиастом проведения таких экспериментов стал Юрий Панчул, - в настоящее время Staff ASIC RTL Design Engineer в компании Juniper Networks (США), а вообще классный специалист в технологиях микросхем.

Он регулярно приезжает в Россию и проводит в Зеленограде школы проектирования на Verilog с упражнениями на платах реконфигурируемой логики ПЛИС.

Мы связались с Юрием и предложили совместно организовать и провести трехдневную школу цифрового проектирования на Verilog в дни проведения выставки ChipEXPO-2020 в Сколково (15-17 сентября).

В этом проекте могут участвовать школьники старших классов (от 9-го и выше) и, если захотят, студенты младших курсов. Школьники до 9-го класса, как правило, недостаточно воспринимают последовательностную логику, хотя мы готовы попробовать с более младшими школьниками, если они пройдут упражнения онлайн-курса, созданного Юрием вместе с РОСНАНО.

К реализации проекта приглашены МИЭТ, ВШЭ МИЭМ и ИТМО, а в качестве помощников - студенты и аспиранты, а также учащиеся физико-математических школ, которые уже принимали участие в зеленоградских школах.

Мы планируем заранее написать инструкции для всех, кто будет вести занятия и помогать в их проведении.

Мы планируем прежде всего привлекать учеников физико-математических школ и победителей олимпиад, но готовы принять и любых школьников и младших студентов, которые пройдут три части теоретического курса от РОСНАНО перед практическими упражнениями в Сколково, под общим названием "Как работают создатели умных наночипов": «От транзистора до микросхемы», «Логическая сторона цифровой схемотехники», «Физическая сторона цифровой схемотехники».

Этот курс необходим, чтобы участники понимали, что они делают, так как время практического семинара ограничено, а информация такого рода сразу в голову не укладывается. По предъявлению сертификата об окончания онлайн-курса, мы, организаторы семинара, будем готовы раздать ограниченное количество FPGA плат, с которыми участники смогут работать дома, до, во время и после семинара в Сколково.

Семинар из трех частей:

2. Создание видеоигры со спрайтами, с выводом из FPGA на VGA монитор.

3. Построение простейшего процессора, на основе проекта schoolRISCV,адаптации процессора schoolMIPS, описанного в недавно вышедшем в ДМК-Пресс учебнике "Цифровой синтез".

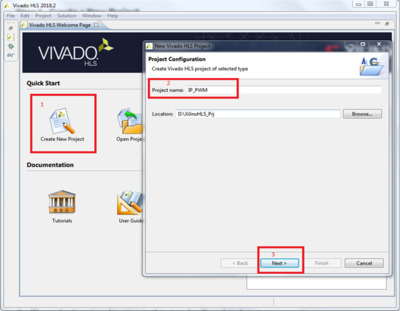

Если говорить о степени владения компьютером, то это не так уж и важно, поскольку все будет показываться в интегрированной среде Intel FPGA / Altera Quartus под Линуксом или Windows. Конечно, если кто-то умеет программировать (например на питоне), то это плюс, но не обязательное условие.

Мы планируем сделать трехдневную школу для одного состава, скажем 20 человек - или больше, если будет много помощников. Параллельно с этим мы можем делать каждый день обзорные лекции для широкой аудитории -

вплоть до 200 человек, если столько наберется. Опыт таких лекций был подтвержден в университете Иннополис - см. Часть 1 и Часть 2.