Сколковская школа синтеза цифровых схем снова открывает свои двери!

Коллеги! В этом году в рамках выставки Чип-Экспо 2021 пройдет очередная "Школа синтеза цифровых схем". Это трех дневный интенсив по проектированию и верификации - это будут две раздельных секции - одна для начинающих , другая для опытных разработчиков. Участие в мероприятии бесплатное. Несколько человек из нашего FPGA комьюнити сделают доклады в рамках школы. Также будет вестись онлайн трансляция мероприятия.

Страница регистрации - начинающим | Программа для опытных разработчиков

Школа синтеза цифровых схем.

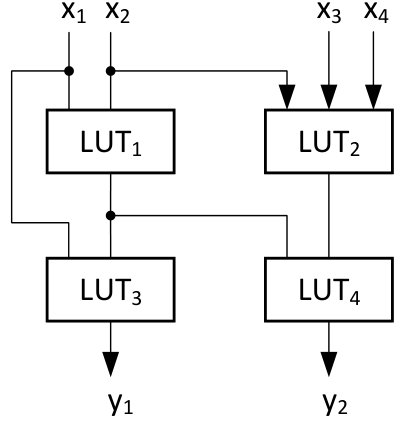

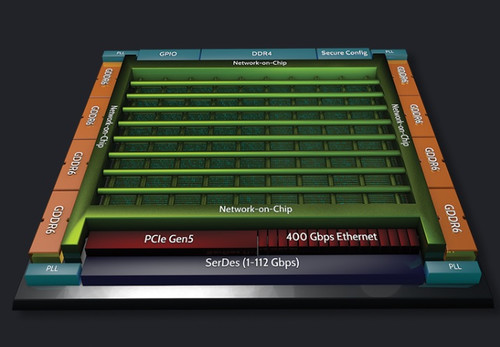

Предназначена для аудитории продвинутых школьников и младших студентов, которые хотят попробовать современную технологию проектирования микросхем в массовых устройствах: синтез из кода на языке описания аппаратуры Verilog. Для реализации схем используются реконфигурируемые микросхемы ПЛИС/FPGA, но те же самые методы применимы и для создания фиксированных микросхем ASIC, которые производятся на фабрике и становятся сердцем смартфонов и игровых приставок, автомобильной и промышленной электроники. Помимо школьников и студентов секция может быть полезна преподавателям физматшкол и руководителям куржков электроники, которые интересуются внедрением преподавания ПЛИС в дополнение к упражнениям с микроконтроллерами и роботикой.

Секция 1. Школа синтеза цифровых схем.

14 сентября. Из чего строится современная цифровая схема.

Модератор дня: Александр Михайлович Силантьев, преподаватель Национального исследовательского университета «Московский институт электронной техники» (МИЭТ).

- 15.00-15.15. Открытие школы. Зачем это нужно? Приветствия.

Александр Биленко, организатор ChipEXPO.

Юрий Панчул, инженер-проектировщик и автор образовательных программ в области микроэлектроники.

Эдмунд Хуменбергер (Edmund Humenberger), президент австрийской компании Symbiotic EDA, специалист по открытым маршрутам проектирования.

- 15.15-16.00. Лекция: Комбинационная логика и ее описание на языке Verilog. Теоретический материал переплетается с демонстрацией синтеза для ПЛИС/FPGA в среде Intel® Quartus® Prime Lite Edition. Александр Михайлович Силантьев.

- 16.00-16.30. Упражнение с логическими элементами

И/ИЛИ/НЕ/ИСКЛЮЧАЮЩЕЕ-ИЛИ, входы которых подсоединены к кнопкам, а выходы к светодиодам платы c ПЛИС.

- 16.30-17.00. Упражнение с выводом буквы на семисегментный индикатор.

- 17.00-17.30. Лекция: Последовательностная логика, которая вводит в схемы память и повторения.

Александр Михайлович Силантьев.

- 17.30-18.00. Упражнение со сдвиговым регистром.

- 18.00-19.00. Упражнение для плат PisWords, RzRd, OMDAZZ и ZEOWAA с Intel FPGA Cyclone IV: Комбинируем сдвиговый регистр и вывод на семисегментный индикатор буквы: получаем вывод на многоразрядный динамический семисегментный индикатор слова (например имени ученика). Упражнение для платы Terasic DE10-Lite с Intel FPGA MAX10: Комбинируем сдвиговый регистр и вывод букв на статический семисегментный индикатор: получаем вывод бегущей строки (например имени ученика).

- 19.00-21.00. Дополнительные упражнения и индивидуальные проекты учеников, с помощью от студентов и аспирантов микроэлектроники от участвующих университетов: МИЭТ, Черниговского НТУ, МИРЭА, ВШЭ МИЭМ, Иннополиса и Самарского Университета.

15 сентября. Приемы и примеры цифрового проектирования на уровне регистровых передач.

Модератор дня: Сергей Анатольевич Иванец, декан факультета электронных и информационных технологий, Черниговский национальный технологический университет, Украина.

- 15.00-15.15. Открытие дня. Что будет после Верилога? Приветствие от Стива Хувера (Steve Hoover), основателя американского стартапа Redwood EDA, создателя платформ Makerchip.com и TL-Verilog.

- 15.00-15.15. Opening of the day. What is coming after Verilog? A greeting from Steve Hoover, the founder of a startup Redwood EDA (USA), a creator of Makerchip.com and TL-Verilog platforms.

- 15.15-15.45. Предисловие к примеру игры: рассказ про генерацию графики на VGA.

Сергей Анатольевич Иванец.

- 15.45-16.00. Упражнение с рисованием на экране разноцветных квадратов и других статических изображений.

- 16.00-16.30. Презентация примера графической игры с параллельно вычисляемыми спрайтами и конечными автоматами для сценария игры. Демонстрация запуска игры на плате Digilent Basys3 с Xilinx FPGA Artix-7. Обсуждение модификации игры с помощью добавления новых спрайтов и изменения сценария.

Михаил Коробков, fpga-systems.ru

- 16.30-17.00. Упражнение с запуском игры на платах PisWords, RzRd, OMDAZZ, ZEOWAA и Terasic DE10-Lite.

Сергей Анатольевич Иванец.

- 17.00-17.30. Предисловие к примеру работы со звуком и светом: рассказ про протоколы SPI и I2S, которые используются в периферийных устройствах: датчике освещения Digilent Pmod ALS, микрофоне Digilent Pmod MIC3 и усилителе Digilent Pmod AMP3. Демонстрация работы датчика освещения. Демонстрация распознавания ноты с помощью измерения периода синусоиды главной гармоники. Для чистого звука период синусоиды можно измерять просто подсчитывая количество тактов (не музыкальных тактов, а тактов 50 MHz генератора на FPGA плате) между моментами пересечения числом, полученным от микрофона, определенного уровня. В качестве источника чистого звука можно использовать либо синтетический звук с телефона, либо звук флейты или блокфлейты.

Семён Москоленко, РТУ МИРЭА, по руководством Евгения Певцова, директор Центра проектирования и доцента РТУ МИРЭА.

Виктор Прутьянов и Владислав Молодцов, МФТИ.

Мария Беличенко, преподаватель игры на флейте, будет играть ноты и короткие мелодии для распознавания FPGA платой.

- 17.30-18.00. Упражнения с генерацией звука или последовательности звуков в ответ на распознанную ноту. Первое упражнение генерирует в ответ ноту, повышенную на определенный интервал от распознанной: на тон, терцию, квинту или октаву, в зависимости от положения переключателей на плате. Второе упражнение использует конечный автомат, чтобы сгенерировать мажорное или минорное трезвучие, либо простую мелодию типа "Вечерний звон", в тональности распознанной ноты.

- 18.00-18.30. Упражнение с распознаванием простой мелодии с помощью конечного автомата и выводом результата распознавания на семисегментный индикатор.

- 18.30-19.00. Упражнение с использованием поворотного энкодера Digilent Pmod ENC для регуляции громкости или высоты генерируемого звука, или, альтернативно, для изменения скорости генерируемой мелодии.

- 19.00-21.00. Дополнительные упражнения и индивидуальные проекты учеников по изменению игры на VGA и примеров распознавания и генерации звука, c помощью от студентов и аспирантов микроэлектроники от участвующих университетов.

16 сентября. Первый шаг в архитектуру и микроархитектуру современных процессоров.

Модератор дня — Александр Юрьевич Романов, к.т.н., доцент Московского института электроники и математики им. А.Н. Тихонова (МИЭМ), Национальный исследовательский университет «Высшая школа экономики» (НИУ ВШЭ).

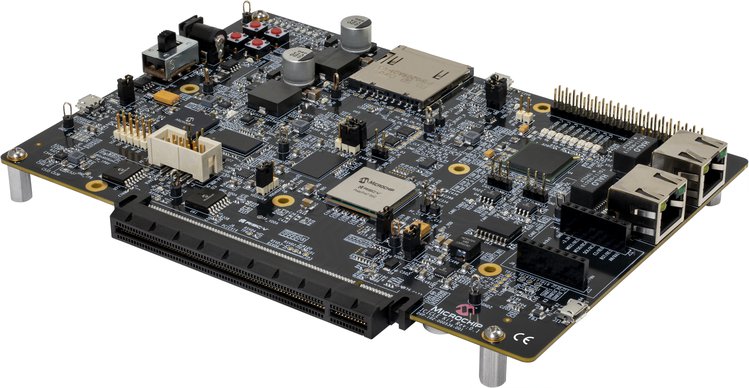

- 15.00-15.15. Открытие дня. RVfpga-SoC: Введение проектирование систем на кристалле (СнК) с использованием ядра CPU и запуском RTOS Zephyr. Презентация Зубаира Какахеля, AZKY Limited, Великобритания, представляющего Imagination Technologies

Зубайр был членом команды MIPS и опытным инженером по совместному проектированию аппаратного и программного обеспечения, с глубоким пониманием взаимодействия между аппаратной реализацией и работающими операционными системами. Он определил проект и стал соавтором RVfpga-SoC для программы Imagination University, которая была выпущена для преподавателей в июле 2021 года.

- 15.00-15.15. Opening of the day. RVfpga-SoC - Introduction to System-on-Chip, "SoC" Design with a real CPU core and running the Zephyr RTOS. Presented by Zubair Kakakhel of AZKY Limited, UK, on behalf of Imagination Technologies.

Zubair was a member of the MIPS team and is an experienced HW-SW Co-design Engineer, with a deep understanding of the interaction between hardware implementation and running operating systems. He defined and co-wrote RVfpga-SoC for the Imagination University Programme which was released to Educators in July 2021.

- 15.15-16.30. Архитектура: вид процессора с точки зрения программиста. Лекция об ассемблере RISC-V с одновременными упражнениями на симуляторе процессора на уровне инструкций.

Никита Поляков, проектировщик микропроцессоров с архитектурой RISC-V в российской компании Syntacore.

- 16.30-18.00. Микроархитектура: вид процессора с точки зрения схемотехника. Лекция по аппаратной организации процессора schoolRISCV, с вариантами одноцикловой и конвейерной микроархитектуры. Демонстрация синтеза процессора и запуск его на платах.

Станислав Жельнио, разработчик микросхем в Syntacore.

- 18.00-19.00. Упражнение по добавлению в процессор инструкции и верификации с помощью программного теста. Измерение максимальной тактовой частоты получившегося варианта процессора.

Станислав Жельнио.

- 19.00-21.00. Дополнительные упражнения и индивидуальные проекты учеников по изменению процессора и интеграции его с периферийными устройствами. С помощью от студентов и аспирантов микроэлектроники от участвующих университетов.

На сайте выставки в разделе «Деловая программа» (http://www.chipexpo.ru/programm) открыт прием Заявок на участие в мероприятиях деловой программы.

Историческая справка:

Verilog HDL (Hardware Description Language) - это язык текстового описания аппаратуры. Он используется для проектирования, моделирования, верификации цифровых микросхем, плат и систем.

Язык Verilog был разработан в 1984-1985 году Филом Морби (Phil Moorby) во время его работы в компании Gateway Design Automation. Тогда же появился первый Верилог симулятор: Verilog-XL. Позже компанию Gateway купила Cadence Design Systems и в 1990-м сделала Verilog HDL публичным достоянием. В стандартом IEEE-1364-1995, IEEE Standard Hardware Description Language Based on the Verilog(R) Hardware Description Language.

Позднее появилась "расширенная" версия языка - это SystemVerilog, разрабатываемый Accellera (www.accellera.org).

В SystemVerilog упор сделан на верификацию проектов, язык содержит элементы объектно-ориентированного программирования.

Как научиться проектировать, моделировать и верифицировать схемы на Verilog?

Главная проблема изучения этого языка для людей, которые уже умеют программировать: Verilog требует другой ментальной модели вычислений. Не цепочки инструкций, как в классических языках программирования, а параллельно работающие облака комбинационной логики, которые хранят состояния в регистрах последовательностной логики.

Чем раньше мозг подсаживается на Verilog - тем лучше. Это как с игрой на скрипке или профессиональным спортом - виртуозы и олимпийские чемпионы занимаются этим с детства. Но как сделать Verilog интересным для школьника? Простые упражнения с мигающими огоньками на платах ПЛИС/FPGA быстро надоедают, упражнения посложнее, типа конструирования процессоров, требуют слишком многих вложений внимания перед тем, как стать интересными. Упражнения с сенсорами типа датчика освещения сводятся к конструированию конечного автомата для протоколов SPI или I2C на ПЛИС и не показывают все аспекты проектирования схем.

После трех лет экспериментирования со школьниками в Москве, Киеве и Новосибирске был найден универсальный способ для быстрого и интересного введения школьника в Verilog с помощью проектирования видеоигр в железе. На этом примере лучше всего усваиваются концепции параллельности, модульной иерархии, проектирования небольшого конвейерного тракта данных и написания конечного автомата для сценария игры. Базовый вариант можно гибко менять, создавая новые игры.

Автором и энтузиастом проведения таких экспериментов стал Юрий Панчул, - в настоящее время Staff ASIC RTL Design Engineer в компании Juniper Networks (США), а вообще классный специалист в технологиях микросхем. Он регулярно приезжает в Россию и проводит в Зеленограде школы проектирования на Verilog с упражнениями на платах реконфигурируемой логики ПЛИС. Мы связались с Юрием и предложили совместно организовать и провести трехдневную школу цифрового проектирования на Verilog в дни проведения выставки ChipEXPO-2020 в Сколково (15-17 сентября)2020 года. Это проект для школьников старших классов (от 9-го и выше) и, если захотят, студентов младших курсов. Школьники до 9-го класса, как правило, недостаточно воспринимают последовательностную логику, хотя мы готовы попробовать с более младшими школьниками, если они пройдут упражнения онлайн-курса, созданного Юрием вместе с РОСНАНО. К реализации проекта приглашены МИЭТ, ВШЭ МИЭМ, ИТМО, МФТИ, ряда университетов и компаний, а в качестве помощников - студенты, аспиранты и учащиеся физико-математических школ, которые уже принимали участие в зеленоградских школах.

Мы планируем заранее написать инструкции для всех, кто будет вести занятия и помогать в их проведении. Мы планируем прежде всего привлекать учеников физико-математических школ и победителей олимпиад, но готовы принять и любых школьников и младших студентов, которые пройдут три части теоретического курса от РОСНАНО перед практическими упражнениями в Сколково, под общим названием "Как работают создатели создатели умных наночипов": «От транзистора до микросхемы», «Логическая сторона цифровой схемотехники», «Физическая сторона цифровой схемотехники». Этот курс необходим, чтобы участники понимали, что они делают, так как время практического курса на мероприятии ограничено, а информация такого рода сразу в голову не укладывается. По предъявлению сертификата об окончания онлайн-курса, мы, организаторы мероприятия, будем готовы бесплатно раздать ограниченное количество FPGA плат, с которыми участники смогут работать дома, до, во время и после мероприятия в Сколково. Для всех остальных, которые захотят пройти курс в "Школе...." мы разместим информацию о том, где можно приобрести платы самостоятельно

Если говорить о степени владения компьютером, то это не так уж и важно, поскольку все будет показываться в интегрированной среде Intel FPGA / Altera Quartus под Линуксом или Windows. Конечно, если кто-то умеет программировать (например на питоне), то это плюс, но не обязательное условие.

Если Вы не хотите (или не можете) стать участником "Школы", можно просто посетить лекции и практические занятия.

Зарегистрироваться для посещения "Школы" можно здесь, заполнив и отправив форму ниже:

В настоящее время достигнута договоренность с Фондом Сколково о том, что "Школа синтеза цифровых схем" будет совместным проектом "ЧипЭКСПО" и Фонда Сколково и проводиться в 2021/2022 году двумя потоками: в октябре-ноябре 2021 года и марте-апреле 2022 года в Технопарке Сколково оффлайн. Занятия продолжительностью 3 часа будут проводиться по субботам. Уже подготовлена программа занятий. Рассматривается возможность вести трансляцию занятий в интернет.