SynthHESer - Новый синтезатор от Aldec

Проекты, описываемые на более высоком уровне абстракции, менее подвержены человеческим ошибкам. Преобразование высокоуровневых описаний в логические элементы осуществляется с помощью инструментов синтеза. Эти инструменты используют различные алгоритмы для оптимизации проекта в целом. Это позволяет обойти проблему различных стилей описания блоков в проекте и неоптимальных методах проектирования. Инструменты логического синтеза также позволяют создавать независимые от технологии конструкции. Технология логического синтеза была коммерциализирована примерно в 2004 году, и с тех пор она стала частью стандартной цепочки инструментов EDA для ASICs и ПЛИС.

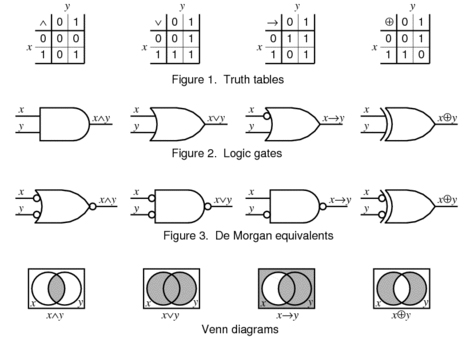

Так что же такое логический синтез? Логический синтез преобразует высокоуровневое описание модуля в оптимизированный список соединений логических элементов (нетлист). Логический синтез использует стандартные библиотеки, в которых описаны простые ячейки, такие как основные логические элементы(и, или и не), или некоторые макроэлементы (сумматор, мультиплексоры, память и триггеры). Стандартные ячейки, собранные вместе, называются технологической библиотекой.

Во многих случаях инструменты синтеза, особенно для ПЛИС, могут стать специфичными для технологии, и это может вызвать проблемы в долгосрочной перспективе с повторным использованием. Здесь, в Aldec, в нашей аппаратной цепочке инструментов мы используем другие инструменты для логического синтеза. Но имея свои собственные инструменты логического синтеза в нашей цепочке инструментов мы обеспечиваем больший контроль и интеграцию с полным маршрутом верификации.

И это то, что мы планируем сделать с нашим продуктом SyntHESer. Это собственный инструмент синтеза компании Aldec для HES-DVM. Мы провели сравнительные тесты и для некоторых проектов он превзошел по скорости Vivado в 10 раз. Он поддерживает General Technology (GTech).

Общие преимущества, которые это приносит нашему инструменту HES-DVM, заключаются в том, что он обеспечивает более быстрый синтез и настройку проекта в HES-DVM. Это позволяет использовать ПЛИС других производителей, помимо Xilinx, и делает HES-DVM не зависимым от сторонних инструментов синтеза. Он также обеспечивает более быструю обработку нетлиста, задействует меньше памяти, улучшенные возможности отладки проекта.

SynthHESer доступен как на Windows, так и на Linux. Он поддерживает все ПЛИС Xilinx 7-й серии, Ultrascale+ . Он также имеет полную интеграцию с Aldec Active-HDL simulator или доступен в автономной версии через командною строку. Он поддерживает различные виды атрибутов для лучшего управления процессом синтеза и имплементации. Он имеет поддержку смешанного синтеза языков для всех стандартов Verilog и VHDL (включая VHDL 2018 и SystemVerilog) и полную поддержку TCL.

Этот новый инструмент можно получить из Active-HDL Design Flow Manager, если вы хотите попробовать его, то запросите бесплатную пробную лицензию

Оригинал