Вебинар: Повышение скорости разработки печатных плат содержащих FPGA

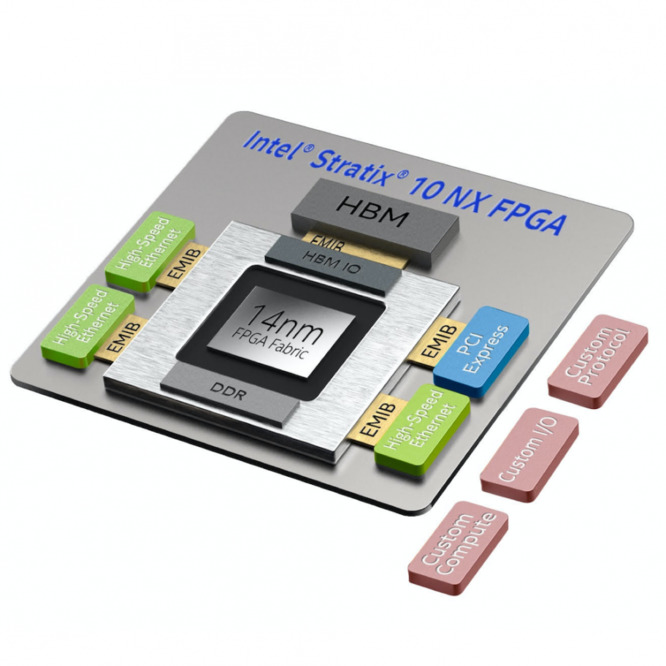

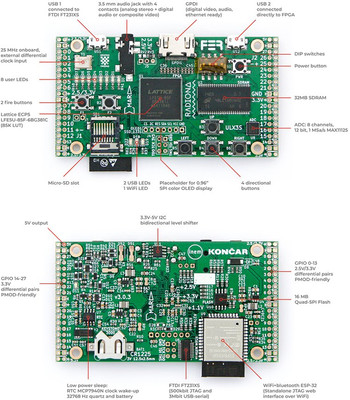

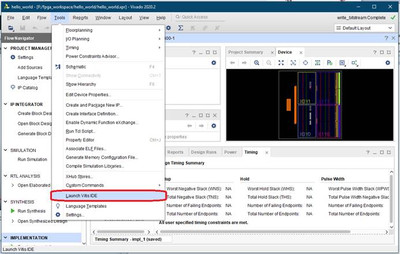

Современные системы требуют современных инструментов оптимизации портов ввода-вывода FPGA, которые бы позволяли быстро выполнять замену контактов (pin swapping) и оптимизацию портов ввода-вывода в рамках процесса проектирования печатных плат.

Дело в том, что отсутствие или плохая оптимизация портов ввода-вывода ПЛИС часто приводит к более длительным циклам/итерациям при трассировке печатной платы и большей длине самих линий, что, в свою очередь, приводит к необходимости дополнительных сигнальных слоев и переходных отверстий, которые могут повлиять на целостность сигнала. Использование инструментов оптимизации портов ввода-вывода FPGA при разработке печатных плат помогает как FPGA так и PCB разработчикам корректно спроектировать печатную плату и учесть все необходимые проектные ограничения.

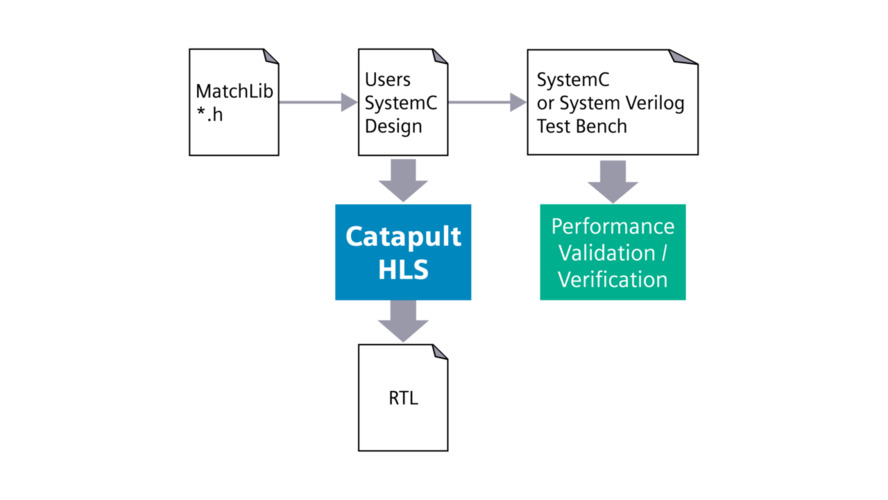

Возможность считывать, экспортировать и синхронизировать файлы HDL и файл проектных ограничений ПЛИС обеспечивает полную согласованность между FPGA и PCB разработчиками в ходе итеративного параллельного процесса проектирования. Это также позволяет создавать печатные платы с FPGA с высоким количеством контактов, используя готовые шаблоны за считанные минуты. Современная оптимизация портов ввода-вывода ПЛИС помогает вам не только ускорить время вывода проекта на рынок, но и снизить производственные затраты.

Вебинар состоится

21 Июля 2020 2:00 PM - 3:00 PM Europe/London регистрация

21 июля 2020 2:00 PM - 3:00 PM US/Eastern

Подробности вебинара и ссылки на регистрацию здесь