«Временные ограничения и анализ в Vivado» – совместный вебинар Макро Групп и PLC2, авторизованного тренинг-партнёра Xilinx

Компания Макро Групп начинает сотрудничество в области обучения технологиям Xilinx с компанией PLC2 GmbH (Германия), авторизованным тренинг-партнёром (ATP) Xilinx. Подготовленные PLC2 тренинги и учебные курсы становятся доступны на территории России и СНГ и проводятся совместными усилиями обеих компаний.

Первый совместный вебинар-тренинг по теме «Временные ограничения и анализ в Vivado» («Vivado Timing Constraints») проводит основатель PLC2 Евгений Красин. Вебинар проходит на английском языке с переводом на русский. В начале вебинара Евгений кратко расскажет о PLC2, её учебных курсах и о сотрудничестве с Макро Групп.

Вебинар состоится 8 декабря 2020 в 11:00 МСК. Продолжительность вебинара – 1,5-2 часа.

Участие бесплатное по предварительной регистрации:

Приглашаем всех заинтересованных специалистов в области проектирования дизайна ПЛИС принять участие в мероприятии.

О теме вебинара

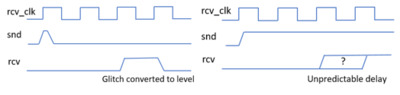

Временные ограничения (timing constraints) используются для задания временных характеристик дизайна. Временные ограничения влияют на все внутренние временные взаимосвязи, задержки в комбинаторной логике (LUT) и между триггерами, регистрами или ОЗУ. Временные ограничения могут быть глобальными или зависящими от пути. Для достижения требуемых временных характеристик проекта, разработчику необходимо задать набор ограничений для этапов синтеза и физической реализации, которые представляют собой требования, предъявляемые к заданным путям или цепям. Ими могут быть период, частота, перекос на шинах, максимальная задержка между конечными точками или максимальная чистая задержка. После синтеза или реализации достигнутые характеристики анализируются с помощью инструментов статического временного анализа Vivado.

Временные ограничения (timing constraints) используются для задания временных характеристик дизайна. Временные ограничения влияют на все внутренние временные взаимосвязи, задержки в комбинаторной логике (LUT) и между триггерами, регистрами или ОЗУ. Временные ограничения могут быть глобальными или зависящими от пути. Для достижения требуемых временных характеристик проекта, разработчику необходимо задать набор ограничений для этапов синтеза и физической реализации, которые представляют собой требования, предъявляемые к заданным путям или цепям. Ими могут быть период, частота, перекос на шинах, максимальная задержка между конечными точками или максимальная чистая задержка. После синтеза или реализации достигнутые характеристики анализируются с помощью инструментов статического временного анализа Vivado.

Статический анализ тайминга – это метод определения соответствия схемы временным ограничениям без необходимости моделирования, поэтому он намного быстрее, чем симуляция с учетом временных задержек. Инструменты Vivado STA проверяют настройки, временные характеристики (setup and hold time), ограничения синхронизации, максимальную частоту и многие другие правила проектирования. Статический анализ тайминга в качестве исходных данных принимает синтезированный список соединений либо физический список соединений проекта. На основе этих списков, алгоритмы Xilinx рассчитывают временные задержки и их соответствие задаваемым разработчиком требованиям.

Вебинар основан на материалах 4-дневного учебного курса «Временные ограничения и анализ в Vivado».