Whitepaper: Оптимизация и применение int4 сверточных нейронных сетей на FPGA Xilinx

Фарш, который творится вокруг нейронных и сетей и их развертывания на ПЛИС ни как не утихает. Всё больше и больше мы видим статей, в которых "магия" целочисленных весов коэффициентов нейронной сети показывает выигрыш на FPGA по сравнению с остальными "альтернативными" вариантами развертывания нейронных сетей.

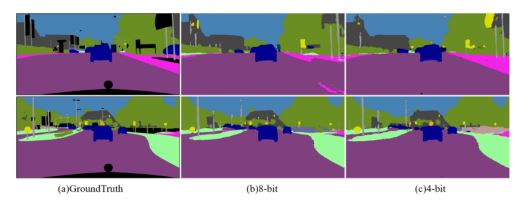

В последнем выпуске белых страниц от компании Xilinx речь идет о применимости нейронных сетей с весами в формате int4 в приложениях автомобильного сегмента и выигрыше, который даёт такая "оптимизация" по сравнению с менее урезанной (int8) и плавающей (fp32) реализациями.

Рекомендуется к прочтению Всем не равнодушно относящимся к CNN на FPGA