Методика работы с Си модулями в симуляции стандартными средствами Vivado

Vivado и SystemVerilog позволяют разработчику использовать модули, написанные на Си. Данный метод называется DPI (Direct Programming Interface). Данная возможность имеет ряд преимуществ:

- В определенных случаях удобнее писать тестбэнч на Си в целях экономии времени

- Если уже есть код на Си, можно его подключить, не переписывая все для симуляции (Это как раз было основной причиной для меня, изучить DPI. В моем случае данные из ПЛИС передаются на компьютер для дальнейшей обработки и что бы просимулировать обработку внутри ПЛИС с обработкой на компьютере одновременно, мне нужно использовать этот метод)

Разберем простейший пример.

В документе ug900 рассмотрен пример использования DPI. Для простоты возьмем его.

1) Создаем проект с именем C_tst_prj

a) Открываем Vivado

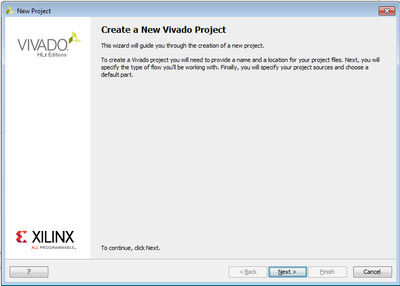

b) Нажимаем Create Project

c) В открывшемся окне нажимаем Next

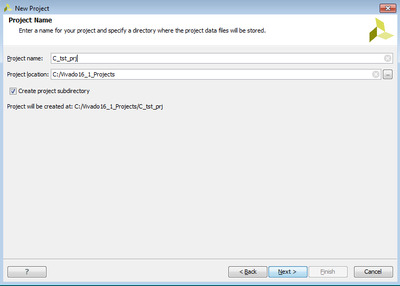

d) Выбираем директорию проекта и вводим его название

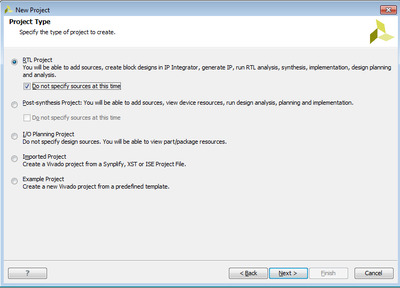

e) Выбираем rtl-проект, ставим галку в указанном поле

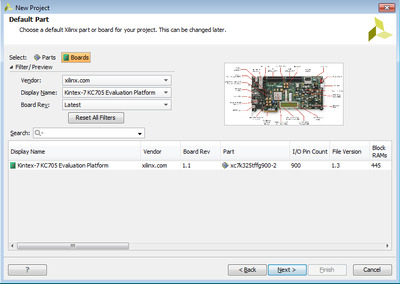

f) Выбираем любую плату – это для нас не важно, так как работа будет производиться исключительно в режиме симуляции.

g) Нажимаем Finish

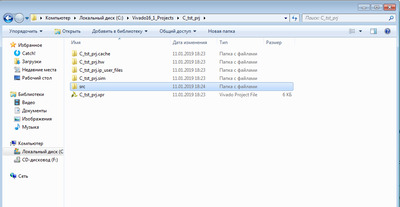

2) В папке проекта создаем папку для исходников src

3) В папке src создаем 3 следующих файла:

function1.c

int myFunction1()

{

return 5;

}

function2.c

#include <stdio.h>

int myFunction2()

{

return 10;

}

file.sv

module m();

import "DPI-C" pure function int myFunction1 ();

import "DPI-C" pure function int myFunction2 ();

integer i, j;

initial

begin

#1;

i = myFunction1();

j = myFunction2();

$display(i, j);

if( i == 5 && j == 10)

$display("PASSED");

else

$display("FAILED");

end

endmodule

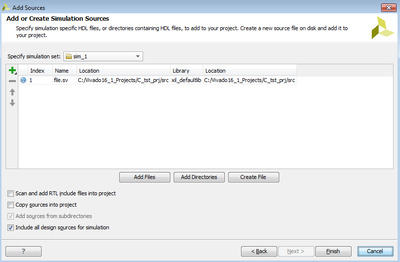

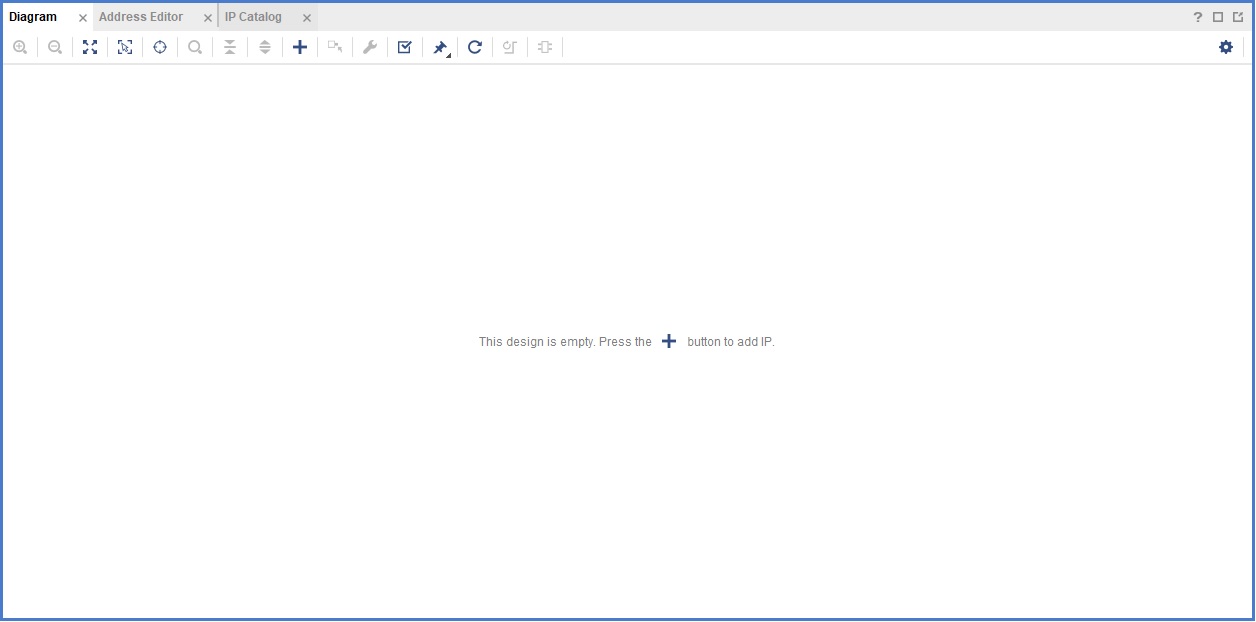

4) Добавляем file.sv в пустой проект в Vivado(File->Add source->Add or create simulation sources->Add, убираем галочку с Copy sources into project, Finish)

Простейший способ запуска симуляции этого проекта команды из консоли:

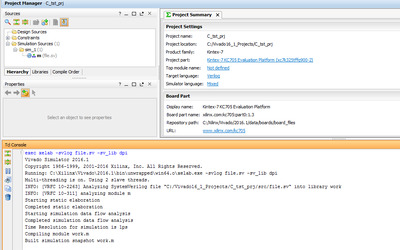

1) В tcl консоли переходим в папку с исходниками (в моем случает это:”cd C:/Vivado16_1_Projects/C_tst_prj/src/”)

2) Выполняем следующие команды:

exec xsc function1.c function2.c – генерируется .so файл и подлинковывается к проекту(если у вас линукс, если windows, то расширение будет .a)

Видим результат исполнения команды:

Done compilation

Done linking: "<Путь к папке проекта>/C_tst_prj/src/xsim.dir/xsc/dpi.so"

exec xelab -svlog file.sv -sv_lib dpi – генерируем снэпшот для симуляции

Результат исполнения команды:

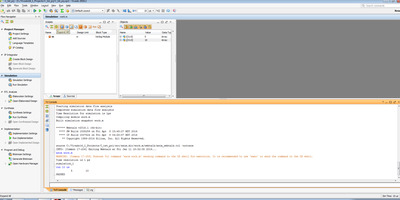

3) Теперь можно запустить симуляцию, воспользуемся штатным xsim, выполняем

xsim work.m

В открывшемся симуляторе нажимаем запуск

Как можно видеть симуляция прошла успешно.

Усложняя этот пример я столкнулся с некоторыми неудобствами – если проект разрастается и в нем появляются xci файлы, это приводит к тому, что эти самые файлы надо перечислять в проекте симуляции, что для меня было совершенно не удобно, так как необходимо было заменять некоторые ядра и запускать симуляцию заново – не удобно каждый раз менять список подлинковываемых файлов. Соответственно есть более удобный метод, не использующий непосредственно команду xelab. В Vivado есть возможность использовать хуки, соответственно этой возможностью я и воспользовался.

Создаем в папке src файл script.tcl в котором будет содержаться всего одна строка:

exec xsc \<Абсолютный путь к файлу>\function1.c \<Абсолютный путь к файлу>\function2.c

*я делал так, но можно привязаться к директории проекта – по желанию

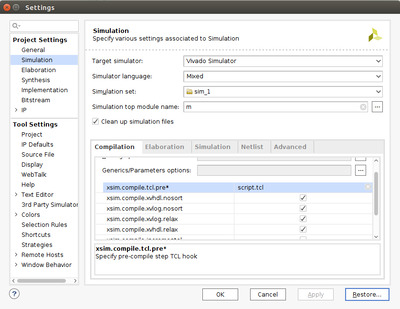

Открывает настройки проекта (Tools -> Settings -> Simulation->Compilation) и в настройках симуляции есть поле xsim.compile.tcl.pre в него добавляем ссылку на script.tcl – таким образом без лишних манипуляций со стороны разработчика .so библиотека будет подлинковываться при нажатии на кнопку симуляции.

*В моем случае я заранее перешел в папку src поэтому ссылка выглядит так.

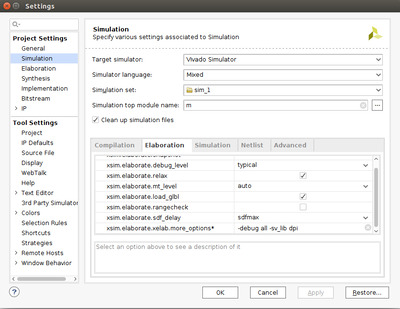

Во вкладке Elaboration в поле xsim.elaborate.xelab.more_options прописываем: “-debug all -sv_lib dpi” – подключение библиотек dpi и включение режима отладки поддерживающего просмотр вэйвформ.

Таким образом теперь симуляцию проекта можно запускать как обычно из gui vivado, а при необходимость добавить Си файл, его нужно просто вписать в файле скрипта, который запускается хуком.

Литература