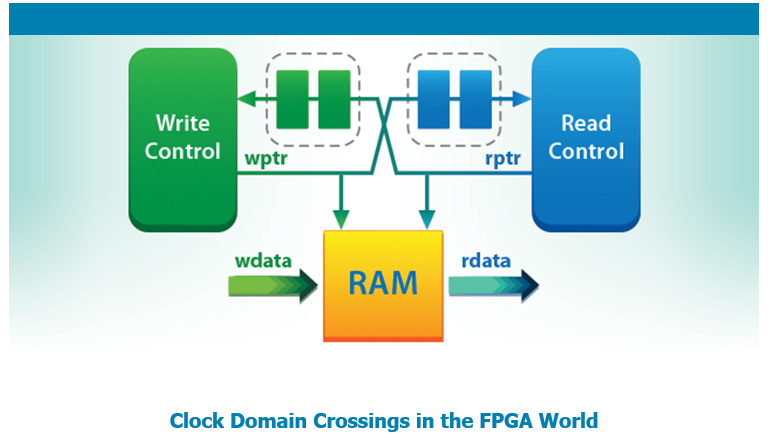

Aldec WP Clock Domain Crossings in the FPGA World

Компания Aldec выпустила документ, рассказывающий об основных ошибках, которые допускают разработчики, когда имеют дело с пересечением тактовых доменов (CDC - Clock Domain Crosing). CDC вызывают наибольшее количество сбоев. Из-за повышающейся сложности и производительности FPGA, влияние ошибок при CDC также увеличивается. В статье рассматриваются вопросы ошибок и их устранение, в случае CDC. Приведены несколько реальных примеров, на которых показаны различные техники работы при пересечении тактовых доменов. В статье обобщены наиболее важные принципы работы с CDC.

Содержание:

| Clock Domain Crossings in the FPGA World | 1 |

| Table of Contents | 2 |

| Overview | 3 |

| The Metastability Effect | 3 |

| Two Flip-Flop Synchronizer as a Common CDC Solution | 6 |

| Safe Synchronizer Implementation in FPGA | 7 |

| Half-Cycle Synchronizers in FPGA | 9 |

| Functional Non-Determinism of CDC Signals | 10 |

| Data Synchronizers | 11 |

| Control-Based Data Synchronizers | 11 |

| FIFO-Based Data Synchronizers | 12 |

| Data Synchronizers Implementation in FPGA | 13 |

| Reset Synchronization in FPGA | 15 |

| Cross-Domain Clocking Techniques for Highly-Reliable FPGA Devices | 16 |

| Summary | 17 |

| About Aldec, Inc. | 17 |

Скачать документ можно здесь. Необходима регистрация.