Инструменты FPGA с открытым исходным кодом и поддержка Renode для MCU Core-V

Как сообщает компания Antmicro, они уже уже более года работают вместе с QuickLogic над поддержкой и разработкой средств проектирования с открытым исходным кодом для их ПЛИС . Это первый случай в истории, когда производитель ПЛИС непосредственно участвует в создании полностью открытых средств проектирования для своих изделий. Простота адаптации внутренней работы Плис к конкретным потребностям прекрасно резонирует с динамично меняющимся ландшафтом машинного обучения (ML), где другие платформы не могут обеспечить требуемую свободу проектирования, а инструменты ПЛИС с открытым исходным кодом являются ключом к созданию новых рабочих процессов, которые полностью используют этот потенциал.

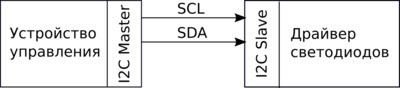

Приверженность QuickLogic и Antmicro к ML с открытым исходным кодом на этом не заканчивается. QuickLogic и Antmicro в настоящее время сотрудничают в направлении создания инструментов моделирования с открытым кодом (Renode), отладочных плат (QuickFeather) и программного обеспечения (Zephyr) для QuickLogic EOS S3 FPGA SoC (построена на ARM) для экосистемы TinyML.

В настоящее время Antmicro делает еще один шаг - в совместном проекте с Google и QuickLogic мы разрабатываем моделирование Renode и поддержку средств проектирования на FPGA для захватывающего проекта MCU Core-V OpenHW Group с ядром CV32E40P RISC-V наряду с efpga от QuickLogic. Опираясь на открытый исходный код RISC-V ISA и FPGA внутри, он будет интересен для приложений TinyML. Он доступен для предкремниевой разработки благодаря поддержке Renode,которая включает в себя возможность совместного моделирования с ПЛИС.

Продолжение см. здесь