Преодоление энергетических, габаритных и других конструктивных ограничений с помощью возможностей Плис

Вебинар компании Lattice

Описание: Технологические тенденции, такие как промышленная автоматизация и 5G, заставляют разработчиков на разных рынках стремиться добавить обработку и подключение к приложениям, работающим на в направлении network Edge. Для успешной поддержки этих тенденций устройствам требуется маломощное вычислительное оборудование с поддержкой популярных интерфейсов, таких как PCIe и Gigabit Ethernet.

Благодаря правильно выбранному соотношению количества портов ввода-вывода к габаритам корпуса, наличию высокоскоростных интерфейсов, надежной аутентификации и шифрованию, ПЛИС Lattice Certus-NX дают разработчикам простое в использовании, маломощное, универсальное решение малого форм-фактора.

Зарегистрируйтесь на этот вебинар, чтобы узнать гораздо больше

Вы узнаете:

- почему Плис Certus-NX являются привлекательным решением для широкого спектра применений, от обработки данных в автоматизированном промышленном оборудовании до управления системами в коммуникационной инфраструктуре;

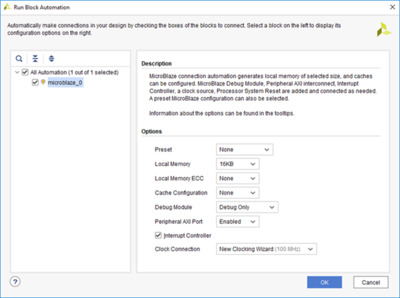

- как Lattice ускоряет разработку систем с помощью простого в использовании оборудования, программного обеспечения и IP-блоков

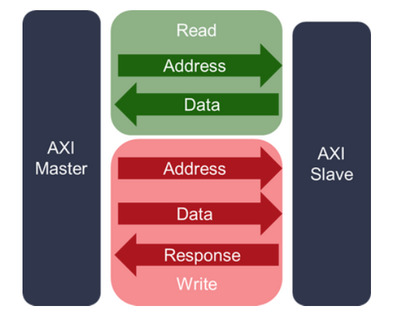

- о PCIe решениях c помощью Certus-NX FPGA

Вебинар состоится: 16 ноября, 2020

Время: 2 PM EST (11 AM PST / 8:00 PM CET)