Для чего мы используем прототипирование FPGA?

Прототипирование FPGA используется для различных целей. Вот 3 его основных применения:

- Отладка FPGA: на определенном этапе цикла проектирования ПЛИС необходимо провести испытания на "реальной" плате, чтобы найти оставшиеся ошибки, не выявленные во время моделирования.

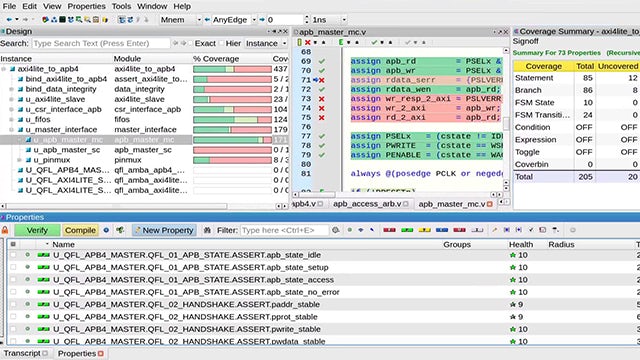

- IP Верификация: целью является проверка аппаратного обеспечения IP, экспериментирование с ним в различных внешних условиях, тестирование сценариев интеграции, стресс-тестирование и, в частности, оценка возможностей производительности IP.

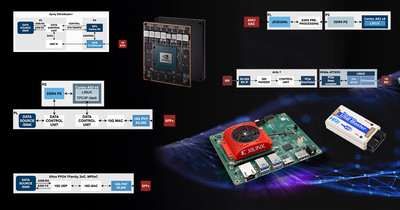

- Проверка ASIC: Перед запуском в производство микросхемы ASIC переносятся на микросхемы FPGA. Это может помочь во многих случаях: от проверки и отладки оборудования до предоставления платформы разработки программного обеспечения для будущего SoC. Термин «Прототипирование FPGA» также обычно понимается как «Прототипирование FPGA под ASIC или SoC».

Более того, поскольку прототипы FPGA потенциально работают намного быстрее, чем эмуляторы и симуляторы, они хорошо подходят для выполнения большого количества циклов. По этой причине они являются важными инструментами для повышения уверенности в том, что FPGA, ASIC или IP поставляются без ошибок в максимальном количестве конфигураций. Таким образом, регрессионное тестирование также является ключевым применением прототипирования ПЛИС.

How do requirements differ according to usage?

В компании Exostiv Labs мы уделяем особое внимание предоставлению лучших инструментов для визуализации ПЛИС. Мы считаем, что достижение задач целевого использования предъявляет определенные требования к платформе прототипирования FPGA и ее инструментальной среде. Я хочу поделиться с вами тем, как мы классифицируем и различаем эти виды использования, основываясь на нашем опыте и отзывах наших клиентов.

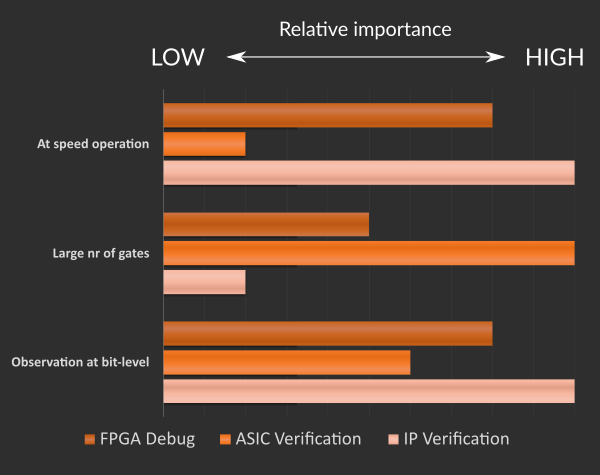

Мы выяснили, что каждое использование характеризуется как минимум 3 параметрами. Относительная важность этих параметров определяет тип платформы для прототипирования ПЛИС, которую следует использовать, и требования к инструментам, используемым вместе с ней.

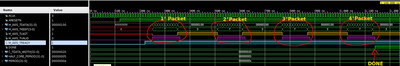

Dimension 1: At speed operation

Первое измерение заключается в том, должен ли прототип работать на целевой скорости - или близко к ней. На самом деле работа прототипа на скорости имеет только преимущества. Во-первых, такой прототип является более точным изображением будущей системы. Во-вторых, "на скорости" позволяет запустить прототип в целевой среде без необходимости использовать ухищрения для замедления его работы. Наконец, количество циклов, выполняемых в секунду, гораздо выше, что приводит к лучшему покрытию. Обычно снижение скорости прототипа - это не желаемая характеристика, а просто ограничение, которое возникает в результате:

- Разбиения на разделы: оно создает "узкие места" для данных на интерфейсах между ПЛИС, вынуждая снижать частоту системы.

- Технологий FPGA: если в прототипе используется более медленный (устаревший) техпроцесс, есть шансы, что он не будет работать на целевой скорости, например, ASIC.

- Возможностей инструментов: если инструменты, поставляемые со средой прототипирования, не могут работать с частотой выше определенной, это ограничение ложится на прототип в качестве ограничения.

При использовании новейших технологий FPGA скорость работы может быть очень высокой, на уровне или очень близкой к будущему чипу, в который интегрировано IP. Когда в прототипе используется интерфейсная IP, работа на высокой скорости может быть даже необходимостью - особенно при тестировании IP с набором реальных периферийных устройств, которые не могут быть замедлены.

Разбиение на разделы и ограничение инструментария могут сделать выполнение прототипа ПЛИС на полной скорости работы просто невозможным, даже при использовании новейших технологий ПЛИС. Обычно разработчикам удается приспособиться к более низкой скорости. Стоит отметить, что даже при скорости 1/100 или 1/1000 от целевой скорости прототипы ПЛИС все равно работают быстрее, чем большинство эмуляторов.

Dimension 2: Required nr of gates

Размер прототипа проекта влияет на требуемое количество вентилей. Если вы превысили размер самой большой микросхемы в конкретной технологии ПЛИС, возникает необходимость в разделении. Чтобы ограничить это, следует использовать самую большую из имеющихся микросхем. Хотя на рынке представлено множество небольших плат FPGA - или их даже можно разработать по разумной цене - крупные системы прототипирования с FPGA с возможностью специального разделения являются скорее специализацией крупных EDA компаний. Когда проектируется система на базе ПЛИС или IP, появляется больше свободы в приобретении платы, которая точно соответствует потребностям прототипирования.

Ограничены ли вы в выборе платы или нет, вопрос об инструментах остается: какой инструмент вы можете использовать с платформой для верификации дизайна и достаточен ли он для ваших нужд?

Dimension 3: Necessity of observation at bit level

Что вы действительно будете делать с прототипом? На что вам нужно обратить внимание и какова ключевая функциональность, которая должна быть выполнена наилучшим образом? Выполнение, по-видимому, является основной функцией прототипа: он должен работать как целевой проект - и это имеет либо проверочную, либо проектную цель. Дизайн должен работать в соответствии со своей спецификацией. Другой основной целью является разработка программного обеспечения - и прототип является первой платформой, на которой программное обеспечение работает с приемлемой скоростью.

В большинстве случаев ASIC представляют собой сборку IP блоков, которые уже должны быть проверены. (В противном случае проектирование на основе IP, которое мы используем последние два десятилетия, не имело бы особого смысла). При верификации ASIC большая часть работы заключается в проверке того, что выбранные IP правильно функционируют вместе как система. По этой причине во время верификации ASIC большая часть работы по наблюдению выполняется на интерфейсах между этими IP. Следовательно, необходимость точного изучения внутренней работы этих IP вплоть до битового уровня более важна при проектировании (и прототипировании) IP, чем при прототипировании целых ASIC.

Приведенный выше график отражает эти соображения.

В заключение нужно сказать, что будь то отладка ПЛИС, проверка ASIC или верификация IP, каждое из этих применений определяет очень специфический "профиль", который необходимо учитывать при выборе платформы для прототипирования ПЛИС.

Оригинал статьи можно найти по ссылке