Разработка на FPGA – Хорошая, плохая и отторгающая

На просторах интернета наткнулся на занятную статейку, которую может быть будет полезно прочитать, перед тем, как погружаться в мир FPGA

Введение

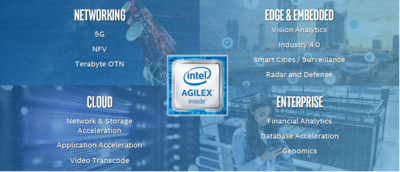

С каждым годом различные журналы и издательства по проектированию встраиваемых систем все чаще говорят о программируемых логических интегральных схемах (ПЛИС). Технология FPGA часто рассматривается как одна из самых мощных, но и одна из самых разочаровывающих этапов для разработчика встраиваемых систем.

С каждым новым поколением FPGA становятся быстрее, имеют меньшую геометрию и меньшее потребление, увеличивается количество логических элементов, улучшается показатель стоимость/количество операций, возможности кажутся бесконечными. Однако с большой мощностью (и реконфигурируемостью) приходят, по крайней мере, с ПЛИС, некоторые серьезные проблемы обучения и разочаровывающие дни (недели) в офисе. Давайте поговорим о том, где сегодня находятся ПЛИС, где они были всего несколько лет назад, и о некоторых болевых точках, которые все еще существуют.

ХОРОШАЯ

Большие, реконфигурируемые, море логических ресурсов

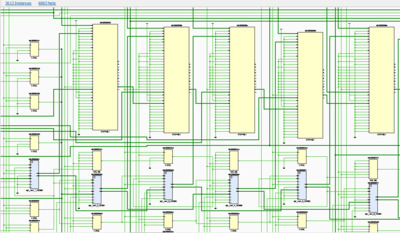

Технология FPGA позволяет разработчику реализовать практически любой алгоритм и/или управление, которые ему требуются. Современная ПЛИС состоит из десятков, а то и миллионов логических элементов и триггеров, которые могут быть объединены вместе, чтобы реализовать всё: начиная от антидребезга для кнопки (denounce circuit) и заканчивая хост-контроллером x16 PCIe gen-3. Использование ПЛИС в вашем проекте дает вам почти бесконечную свободу для реализации любой необходимой вам функциональности.

Уровень абстракции

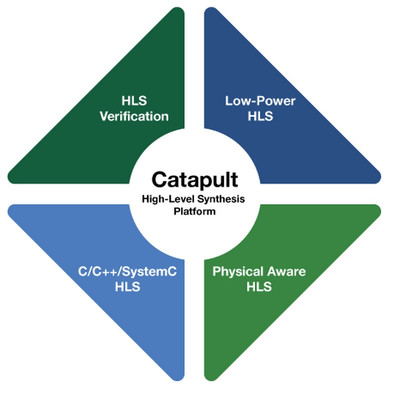

Представьте себе, что вы хотите спроектировать систему на логических микросхемах 74-ой серии, и люди, которые работали с первыми ПЛИС, должны были сделать почти то же самое. К счастью, сегодня нам не приходится думать на таком низком уровне. Существуют языки, называемые языками описания аппаратного обеспечения (HDL – Hardware Description Language), которые помогают разработчикам описать их алгоритм и передать его синтезатору, который затем создает список соединений логических выражений и регистров (нетлист). Кроме того, существует широкий спектр технологий и языков абстракции более высокого уровня. Xilinx предоставляет инструмент под названием Vivado HLS (HLS расшифровывается как high-level synthesis – высокоуровневый синтез), который позволяет разработчику писать на C, C++ или System C и затем из этого описания генерировать HDL код на языках VHDL или Verilog. Здесь, в Viewpoint Systems, мы часто используем технологию LabVIEW FPGA, которая позволяет описывать проект на ПЛИС с помощью графической среды программирования, использующей парадигмы потока данных.

Ресурсы и экосистема

Коммерчески доступные ПЛИС существуют с середины 1980-х гг. это долгий срок для развития технологии и её экосистемы. Существует множество ресурсов, доступных для всего: от понимания того, как устроен кремний, до того, как синтезатор генерирует нетлист, до лучших методологий описания HDL-кода для генерации логических структур, необходимых вам. Вы можете зайти на Amazon и поискать книги по ключевому слову FPGA и найдёте сотни доступных книг. Если вы загуглите слово FPGA, вы сможете найти десятки тысяч ответов на вопросы. Поскольку HDL является текстовым описанием, эти вопросы и ответы индексируются поисковыми системами, что делает поиск информации простым и быстрым.

Кроме того, за последние несколько лет появилось больше ресурсов об инструментах синтеза более высокого уровня, таких как Vivado HLS, Calypto/Catapult и LabVIEW FPGA.

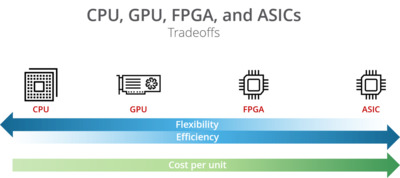

Скорость и размеры

Современные ПЛИС могут работать очень быстро – например, с частотой в сотни мегагерц. Вы можете подумать: "но, мой процессор Intel работает на гигагерцовой частоте!” Это правда! Однако ваш процессор Intel является "процессором общего назначения" – он делает большое количество вещей довольно хорошо, а не небольшое количество вещей действительно хорошо. ПЛИС позволяют писать массово параллельные реализации алгоритмов, при этом пропускная способность может быть в 10 раз, 100 раз или 1000 раз выше, чем любого процессора на современном рынке.

Хотя высокоуровневая абстракция отлично подходит для более быстрого вывода продукта на рынок (time-to-market ) вы просто никогда не сможете заставить свой проект работать так же быстро, как при написании кода вручную в традиционном HDL, таком как VHDL или Verilog. Языки абстракции и технологии высокоуровнего синтеза могут быть великолепны для быстрого создания прототипа; однако неизбежные накладные расходы всегда будут делать ваш проект более ресурсозатратным и, следовательно, более медленным (более низкая максимальная тактовая частота).

ПЛОХАЯ

Кривая обучения

Любой, кто регулярно работает с ПЛИС, скажет вам, что кривая обучения довольно крутая. Этот довольно неудачный аспект работы с ПЛИС означает, что те, кто хочет войти в мир проектирования на ПЛИС, должен либо пройти обширную подготовку (что может быть довольно дорогостоящим - до 1500 долларов за курс), либо быть очень замотивированным в обучении.

“Это работает в симуляторе”

HDL-код по своей сути страдает от необходимости быть написанным и протестированным на другой платформе, в отличие от той, на которой он будет “запущен”. В случае VHDL очень легко написать VHDL-код, который прекрасно работает в моделировании, но никогда не будет работать в железе (загруженным в ПЛИС). Например, попытка сделать слишком много операций за один так (например, выполнение десятков или сотен операций умножения с накоплением (MAC) для фильтра с конечной импульсной характеристики (FIR)).

Маршрут проектирования на HDL выглядит примерно так:

1. Определите входы/выходы разрабатываемого модуля

2. Определите алгоритм и последовательность действий, которые должен выполнять разрабатываемый модуль

3. Составьте структурную схему или блок диаграмму различных частей проекта

4. Если возможно, распишите состояния конечных автоматов и транзакции

5. Напишите код

6. Проверьте синтаксис

7. Выполните моделирование

8. Проверьте корректность работы модуля

--- Если не работает, вернитесь к шагу 5

9. Загрузите файл конфигурации в ПЛИС для тестирования

10. Убедитесь в корректности работы модуля в железе

--- Если не работает, вернитесь к шагу 5

Проблема заключается в том, что вы можете застрять в порочном круге 10 -> 5 снова и снова, пока не сведете себя с ума. Очень большая часть того, чтобы быть опытным разработчиком ПЛИС и программистом, - это знание того, что на самом деле создает код, который вы пишете. Это означает последовательную проверку схемы, сгенерированной вашим кодом, и написание как можно более мелких модулей (это также облегчает тестирование!).

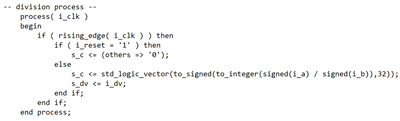

Кроме того, легко написать код, который породит огромное количество логики с помощью всего одной строки. Вот вам пример:

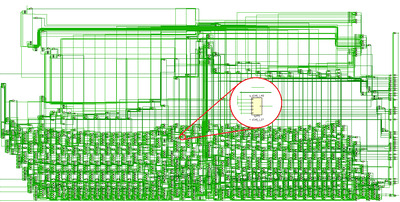

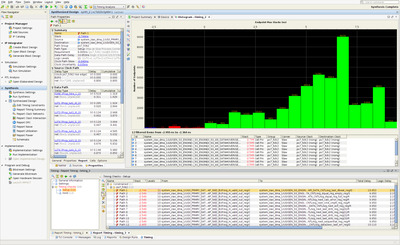

Приведенный выше код генерирует эту схему:

Vivado создала делитель, как мы и хотели, но для этого потребовалось почти 1800 логических ячеек. Сведение временных характеристик (таймингов) выполнения этой операции может оказаться очень сложным, особенно если она является частью других логических операций, которые должны произойти в том же такте.

ОТТОРГАЮЩАЯ

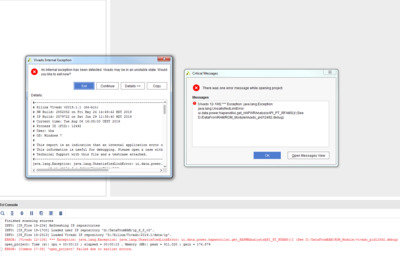

Не совершенность инструментов

Нет ничего более разочаровывающего, чем то, что среда разработки и ее инструменты не делают того, чего вы от них ожидаете или даёт непредсказуемые результаты. Хотя коммерческие ПЛИС существуют уже довольно давно, некоторые аспекты все еще отсутствуют. С последней версией инструментов Xilinx, Vivado, индустрия увидела большой скачок в функциональности и функциях. Это среда новая и она почти полностью заменяет их устаревшие среда разработки, при этом имеет свой собственный набор проблем и ошибок. Altera, производитель ПЛИС номер два, все еще работает с тем же программным обеспечением, который они используют уже более десяти лет.

Сведение таймингов

Тайминги. Тьфу. Я, вероятно, провел большую часть времени, разочаровываясь в проектировании на ПЛИС, когда речь заходит о какой-то маленькой цепочки в нетлисте, которая просто отказывается соответствовать временным ограничениям, независимо от того, что я с ней делаю. Эти маленькие "занозы" появляются постоянно и лучший способ вытащить их – это просто накопленный годами опыт. У Xilinx есть их методология UltraFast Design Methodology, а у 2Altera много документации из серии «best practices», но на самом деле, когда дело доходит до этого, все сводится к написанию хорошего, небольшого, синтезируемого HDL кода. Но несмотря ни на что, вы окажетесь в ситуации, когда вам нужно создать экземпляр 32 чего-то там, и сведение таймингов будет вашим кошмаром.

ЛИЧНО ОТ МЕНЯ

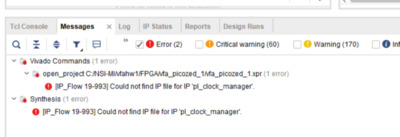

Несовместимость версий IP

Это, наверное, одна из самых раздражающих вещей при проектировании на ПЛИС. Несовместимость релизов среды разработки и используемых IP ядер. Да такое не очень часто случается, но это случается. Бывает так, что IP ядра обновляются, у них появляются новые возможности, но при этом они также могут быть переведены в статус устаревших и неподдерживаемых новой версией среды разработки. По этой причине, многие разработчики отказываются переходить на новую версию ПО в текущем проекте и предпочитают оставаться на изначально выбранной версии ПО. Как говориться, работает не трогай.

Долгая имплементация

Если проект по уровню немного выше среднего, то приготовьтесь к долгим перерывм между итерациями. Сложно сказать, это хорошо или плохо. С одной стороны многочасовая имплементация проекта даёт Вам кучу «свободного», которое можно потратить на написание документации, ревью кода, чтение литературы, просмотр ютубчика. Правда, когда это становится невыносимо, это может побудить разработчика на поиск способов сокращения времени имплементации и он откроет для себя инкрементную имплементацию, ECO-Flow, частичную реконфигурацию и много чего еще другого.

Но, когда горят сроки сдачи проекта, время необходимое на трассировку и размещение проекта, будет утекать как зарплата инженера-разработчика ПЛИС, что приведёт к куче пепла под Вашим рабочим местом, благодаря перегоревшему пукану и облысевшей/поседевшей голове.

Нужен мощный ПК

Современные среды проектирования требуют достаточно мощных (даже по современным меркам) компьютеров для комфортной работы. Не думайте, что если являетесь счастливым обладателем SSD и 16ГБ оперативы, то вам этого хватит. Боль и ужас от тормознутости интерфейса при таких параметрах заставят вас отказаться от покупки новой видеокарты для «Crysis на максималках» в пользу лишней планки и еще одного SSD для ваших ПЛИСовых проектов. Более того, если раньше для установки того же ISE вам бы хватило на «долгую счастливую жизнь» 10-20ГБ места на жёстком диске, то сейчас, только для установки желательно иметь не меньше сотни ГБ свободного места. Ну и под место под проекты не стоит забывать.

Я уверен, что мы что-то упустили, напишите в комментариях что именно и мы будем потихоньку дополнять эту статью новыми «радужными» аспектами проектирования на FPGA