ПЛИС и АЦП :: 1000 и 1 способ реализации SPI :: Часть 1

Первый стрим в этом году мы начнем с рубрики "ПЛИСдатые самоделки". Те кто давно на канале наверняка видели первые два видео про работу с интерфейсом SPI - курс для начинающих, который так и остался не законченным

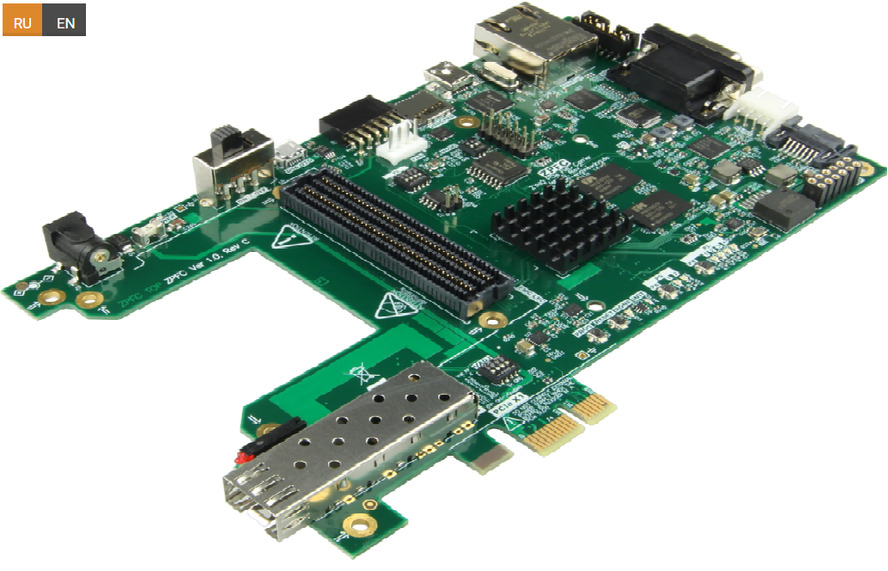

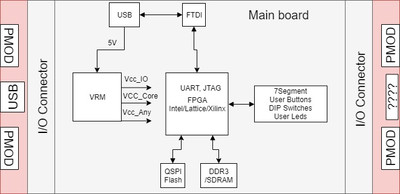

НО! Удачно найденная отладочка на aliexpress со всем необходимым для продолжения курса прибыла как раз перед новым годом и теперь мы можем убить двух зайцев сразу: закончить серию видеоуроков по SPI и провести FPGA стрим.

На модуле с алика есть всё необходимое: MCP3201 - тот самый АЦП из курса по SPI, аудио гнездо 3,5мм для подключения аналогового аудиосигнала, дополнительные компоненты в виде операционника, источника опорного напряжения и всякой прочей рассыпухи.

Стримов по работе с #SPI АЦП будет несколько, а закончатся они рабочим макетом цветомузыки на FPGA. Сегодня мы займёмся разработкой поведенческой модели АЦП #MCP3201 на VHDL и Verilog и скорее всего успеем сделать один из вариантов реализации интерфейса SPI.

Ссылка на отладку с АЦП

Интерфейсы :: SPI :: Часть 1:: Общие сведения

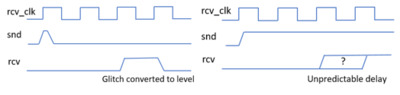

Интерфейсы :: SPI :: Часть 2:: Варианты реализации

Каждую субботу в 20:00 #FPGA стримы, заходи тут интересно