Вебинар: Интегрирование Arm Cotex-M3 в ПЛИС Xilinx

06.04.2020 16:43

2641

0

0.0

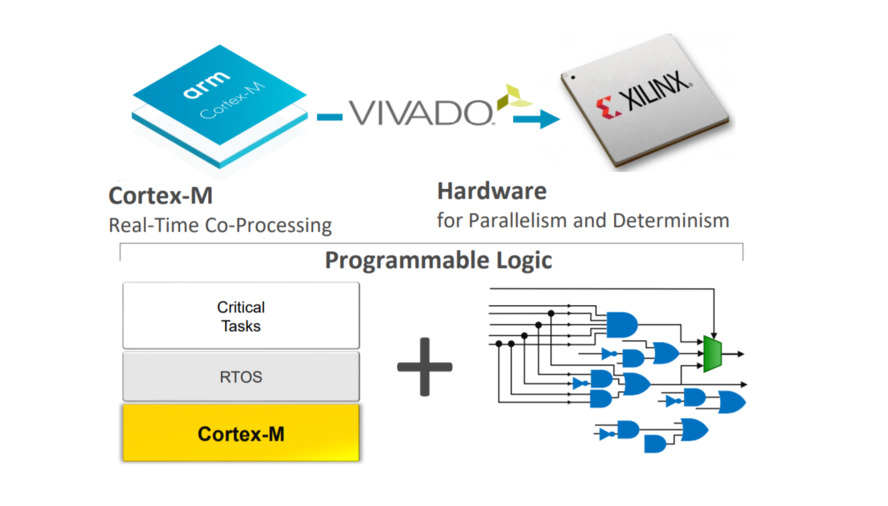

Лучшее решение для встраиваемых систем

Комбинирование широко известного микроконтроллера с архитектурой Arm® Cortex®-M и производительных FPGA компании Xilinx даёт разработчикам гибкость и простор для инновационных решений при разработке устройств.

Многие пользователи Vivado уже знакомы или уже используют процессор MicroBlaze, выполненный по архитектуре RISC. Однако Arm Cortex-M3 имеет существенно иную аппаратную архитектуру, с уникальными аспектами системной интеграции.

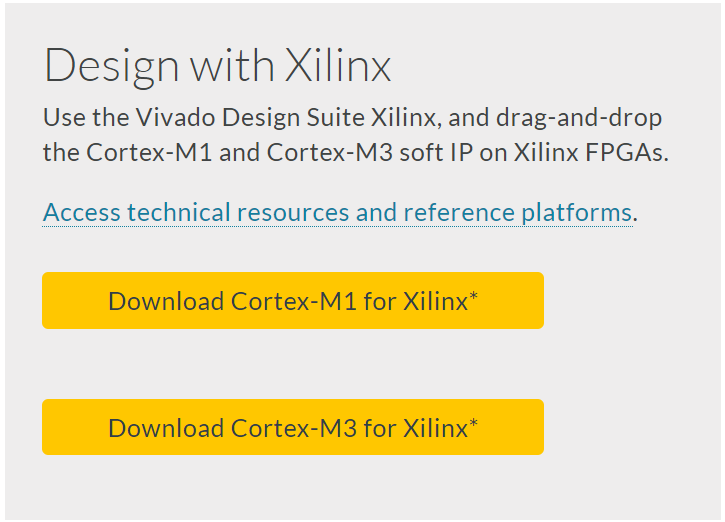

На этом вебинаре мы рассмотрим IP-блок Cortex-M3 и обсудим его интеграцию внутри ПЛИС Xilinx. Мы обсудим:

Время проведения: 12-1pm (BST); 1-2pm (CEST); 4.30-5.30pm (IST)

Подробности и ссылка на регистрацию

Комбинирование широко известного микроконтроллера с архитектурой Arm® Cortex®-M и производительных FPGA компании Xilinx даёт разработчикам гибкость и простор для инновационных решений при разработке устройств.

Многие пользователи Vivado уже знакомы или уже используют процессор MicroBlaze, выполненный по архитектуре RISC. Однако Arm Cortex-M3 имеет существенно иную аппаратную архитектуру, с уникальными аспектами системной интеграции.

На этом вебинаре мы рассмотрим IP-блок Cortex-M3 и обсудим его интеграцию внутри ПЛИС Xilinx. Мы обсудим:

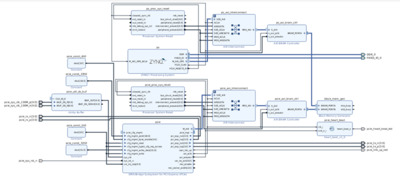

- две основные системные шины, модель их использования и ограничения

- работу контроллера приоритетных векторных прерываний (NVIC - Nested Vectored Interrupt Controller) и его взаимодействие с Wakeup Interrupt Controller (WIC)

- операции управления памятью наряду с инвазивными и неинвазивными функциями отладки ядра

Время проведения: 12-1pm (BST); 1-2pm (CEST); 4.30-5.30pm (IST)

Подробности и ссылка на регистрацию

A best-of-both worlds solution for embedded systems

The combination of the widely acclaimed Arm® Cortex®-M MCU architecture with the performance of a Xilinx® FPGA provides more flexibility and greater scope for innovation in the creation of application-optimised designs.

Many Vivado® users are familiar with the Microblaze™ RISC processor. However, the Arm Cortex-M3 has a substantially different hardware architecture, with unique system integration aspects.

In this webinar we will examine the Cortex-M3 IP block and discuss its integration inside a Xilinx FPGA. We will:

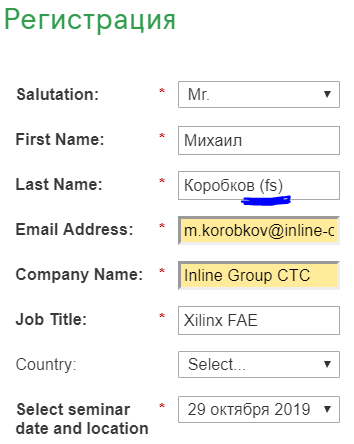

Extra session for Europe and Asia:

For Americas

The combination of the widely acclaimed Arm® Cortex®-M MCU architecture with the performance of a Xilinx® FPGA provides more flexibility and greater scope for innovation in the creation of application-optimised designs.

Many Vivado® users are familiar with the Microblaze™ RISC processor. However, the Arm Cortex-M3 has a substantially different hardware architecture, with unique system integration aspects.

In this webinar we will examine the Cortex-M3 IP block and discuss its integration inside a Xilinx FPGA. We will:

- Examine the two main system busses, their use model and restrictions

- Review the operations of the Nested Vectored Interrupt Controller (NVIC) and its interaction with a Wakeup Interrupt Controller (WIC)

- Examine the memory management operations along with invasive and non-invasive debugging features of the core.

Extra session for Europe and Asia:

- Wednesday April 8, 2020

Time: 12-1pm (BST) 1-2pm (CEST)

1-2pm (CEST)  4.30-5.30pm (IST)

4.30-5.30pm (IST)

For Americas

- Wednesday April 8, 2020

Time: 10-11am (PDT) 11am-12pm (MDT)

11am-12pm (MDT)  12-1pm (CDT)

12-1pm (CDT)  1-2pm (EDT)

1-2pm (EDT)