Запись вебинара:Высокоуровневое проектирование на платформе Xilinx

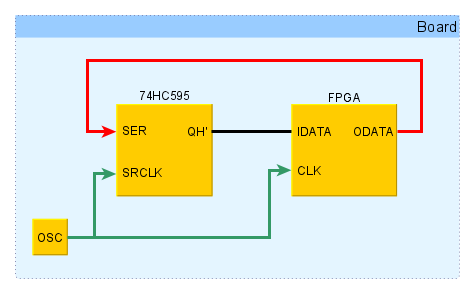

Долгие годы проектирование для ПЛИС было очень трудным делом, а многие этапы этого процесса напоминали белую и черную магию. Рисунок хорошо иллюстрирует один из методов работы специалистов по ПЛИС «старой закалки».