Статьи из категории: Видеоуроки

Категория:Видеоуроки

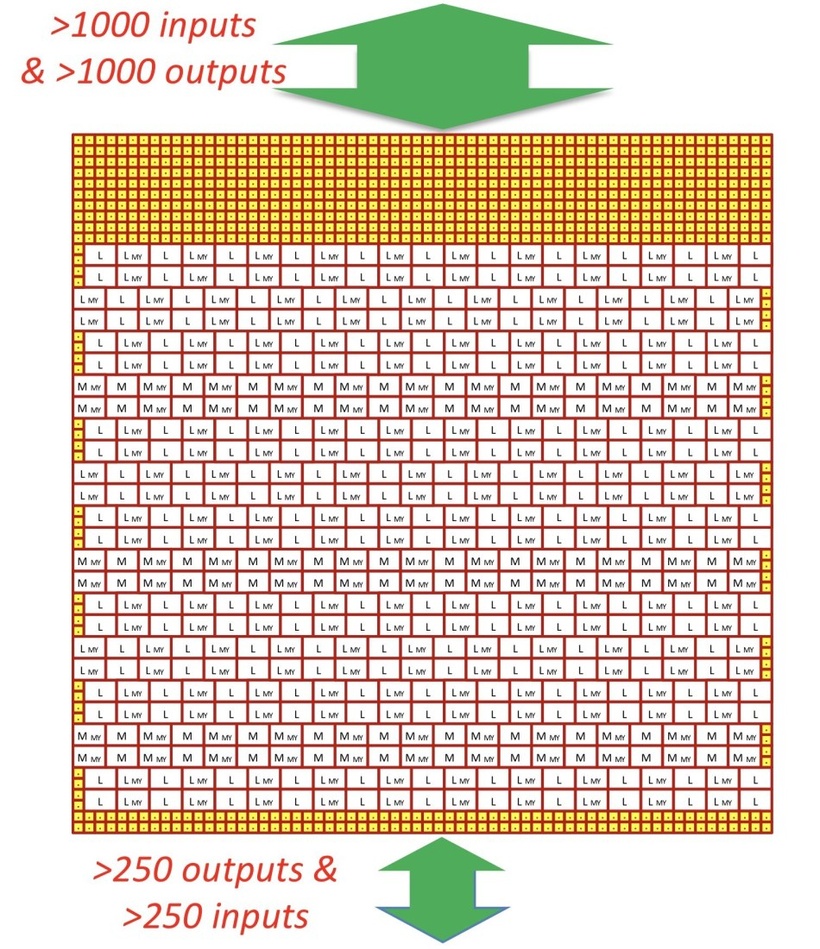

FPGA начального уровня :: Часть 5.1 :: Подключение портов к ножкам ПЛИС и размещение проекта на кристалле

Здравствуйте друзья. С вами проект http://fpga-systems.ru. Мы продолжаем курс лекций по проектированию на FPGA для разработчиков начального уровня. Сегодня мы с Вами приступим с размещению нашего проекта на кристалле и привязке ножек нашей ПЛИС к портам модуля верхнего уровня нашего проекта.

Ссылки на документацию см. ниже

5346

FPGA начального уровня :: Часть 4 :: Сборка процессорной системы на MicroBlaze

Здравствуйте друзья. С вами проект FPGA-Systems.ru. Мы продолжаем курс лекций по проектированию на FPGA для разработчиков начального уровня. Сегодня, в 4-ой части нашего видеокурса, мы с Вами приступим с сборке процессорной системы на базе софт процессора MicroBlaze, а также объединим его с нашей разработанной физически неклонируемой функцией Arbiter PUF.

4454

0

FPGA начального уровня :: Часть 3.3 :: Разработка PUF на HDL

Здравствуйте друзья. C вами проект http://fpga-systems.ru. Мы продолжаем курс по проектированию на FPGA для разработчиков начального уровня. В этом видео мы продолжаем разрабатывать HDL код для физически неклонируемой функции Arbiter PUF. Сегодня мы спроектируем D-триггер и разработаем проект верхнего уровня для Arbiter PUF. Несмотря на то, что это видео является заключительным видео третьей части, не стоит расслабляться, поскольку это всего лишь не более 20 процентов от всего проекта. Нам ещё многое предстоит сделать и многому научиться.

Следите за выходом новых видео на канале в Telegram

FPGA-Systems.ru Events

https://t.me/Powered_by_KeisN13_events

Обсуждайте в чате Telegram FPGA-Systems.ru

https://t.me/Powered_by_KeisN13

4516

0

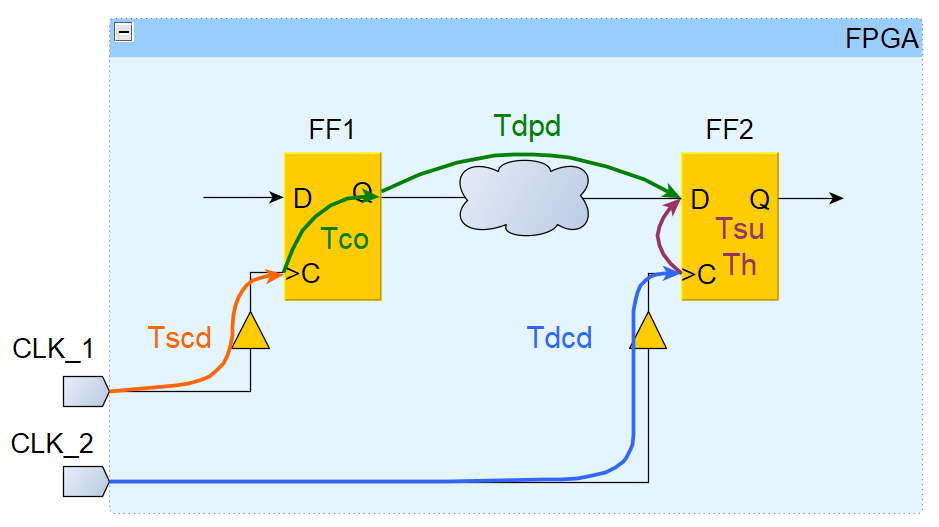

FPGA начального уровня :: Часть 3.2 :: Разработка PUF на HDL

В этом видео мы продолжаем разрабатывать HDL код для физически неклонируемой функции Arbiter PUF. Сегодня мы спроектируем линию задержки, основой которой послужит разработанный на прошлом занятии мультиплексор.

3377

0

FPGA начального уровня :: Часть 3.1 :: Разработка PUF на HDL

Здравствуйте друзья. C вами проект http://fpga-systems.ru. Мы продолжаем курс по проектированию на FPGA для разработчиков начального уровня.

В этом видео мы приступаем к разработке HDL кода и реализуем один из самых простых компонентов Arbiter PUF - мультиплексор.

Мы подробно проходим по каждому этапу проектирования: начиная от создания каталога и проекта в среде Xilinx Vivado и заканчивая анализом результатов синтеза.

Разработка ведется как на VHDL так и на Verilog, поэтому ни кто не останется в обиде. В целом всё очень схоже, в чём Вы сами сможете убедиться.

4349

0

FPGA начального уровня :: часть 2 :: PUF и структура проекта

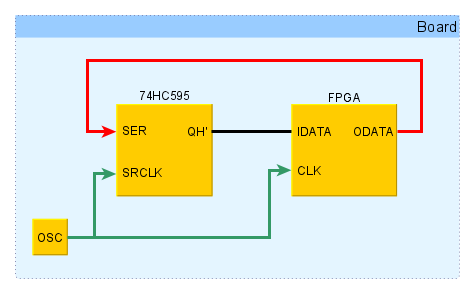

Здравствуйте друзья. Мы продолжаем курс лекций по проектированию на FPGA для разработчиков начального уровня. Сегодня мы с Вами рассмотрим что такое физически неклонируемая функция и обсудим структуру предстоящего проекта.

4328

0

FPGA начального уровня :: Часть 1 :: Обзор

Здравствуйте друзья. Представляем Вам курс по проектированию на FPGA для разработчиков начального уровня.

6667

0

0