Архив новостей из мира FPGA

Бесплатные тренинги от Intel на июль

Товарищи, если вы сможете попасть на эти тренинги, поделитесь, пжлст, материалами тренинга или их записью с FPGA коммунити. Напишите мне в телегам @KeisN13 или почту admin@fpga-systems.ru Давайте сделаем бесплатные материалы тренингов доступными для всех.

4959

Российский форум «Микроэлектроника» - межотраслевая площадка для общения специалистов в области разработки, поставки и применения ЭКБ и РЭС

С 9 по 14 октября 2023 года в Парке науки и искусства «Сириус» пройдет одно из важнейших событий года в сфере высоких технологий − Российский форум «Микроэлектроника 2023», ставший основной межотраслевой площадкой для ... Читать дальше »

6377

0

AMD анонсирует самый ёмкий FPGA чип

Компания AMD / Xilinx не перестаёт нас радовать покорением новых вершин. Вслед за недавним анонсом Spartan US+ мы в первом-втором квартале 2024 сможем лицезреть монстра серии Versal - VP1902,которая должна стать самой ёмк ... Читать дальше »

3223

0

AMD / Xilinx анонсирует Spartan US+

Компания AMD анонсировала ПЛИС Spartan™ UltraScale+™. Пока кроме общепринятого "идеально подходит для экономичных приложений, требующих низкого энергопотребления и высокоскоростных пртов ввода-вывода, и предназначено для широкого спектра отраслей, включая промышленность, робототехнику, "Ум ... Читать дальше »

2928

0

ExpoElectronica 2023: о Премии Electronica

Успейте до 17 марта подать заявку на участие в Премии Electronica, и представить последние достижения вашей компании целевой аудитории.

Главная цель Премии - п ... Читать дальше »

1213

0

Релиз Chisel v3.6.0-RC2

Разработчики языка генерации аппаратуры Chisel выпустили в свет новую версию 3.6.0.

Версия примечательна прежде всего тем, что в ней заменили компилятор ... Читать дальше »

2887

0

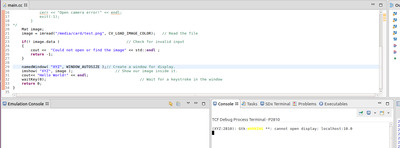

Двухдневный семинар "Использование приложений видения с KRIA" (день 2)

Этот семинар посвящен Kria ™ System-on-Module (SOM) и Kria KV260 Vision AI Starter Kit от AMD Xilinx.

Мы расскажем как ускорить работу vision-приложений, используя KV260 Starter Kit прямо из коробки без каких-либо знаний FPGA.

...

Читать дальше »

6350

0

Двухдневный семинар "Использование приложений видения с KRIA" (день 1)

Этот семинар посвящен Kria ™ System-on-Module (SOM) и Kria KV260 Vision AI Starter Kit от AMD Xilinx.

Мы расскажем как ускорить работу vision-приложений, используя KV260 Starter Kit прямо из коробки без каких-либо знаний FPGA.

...

Читать дальше »

6259

0

Начало работы с UVM

Цель вебинара предоставить вам базу для начала изучения UVM, начиная с того, почему стоит ее использовать заканчивая описанием ключевых компонентов UVM тестбенча. На вебинаре будет представлен обзор интерфейса DUT и его взаимодействие между секвенсором и драйвером.

Мы рассмотрим:

6382

0

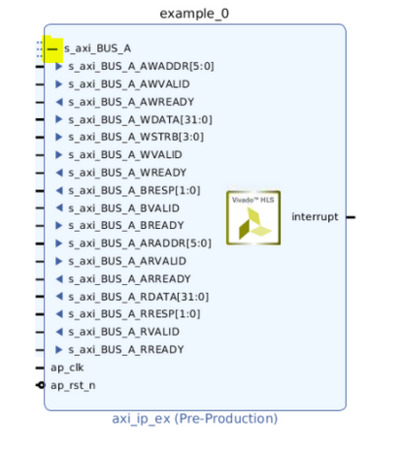

Высокоуровневый синтез для исследования архитектуры аппаратного/программного обеспечения для инференса

Периферийные устройства всех типов становятся умнее, благодаря способности слушать нас, понимать наши жесты и даже распознавать нас. Этот интеллект исходит из возможностей глубоких нейронных сетей. Обработка данных требует больших вычислительных затрат и может легко перегружать встроенные процессоры при огранич ... Читать дальше »

6203

0

0