Архив новостей из мира FPGA

Более 3 тысяч участников посетят мероприятия форума «Микроэлектроника 2024»

**Представители средств массовой информации смогут зарегистрироваться на форум с 11 по 23 сентября

С 23 по 28 сентября на площадке Научно-технологического университета «Сириус» пройдет Российский ... Читать дальше »

2758

Юбилейный Российский форум «Микроэлектроника 2024»: 10 лет развития и успеха!

Ключевое информационное событие года в сфере электронных технологий – Российский форум «Микроэлектроника 2024», пройдет с 23 по 28 сентября 2024 года на Федеральной территории «Сириус».

4013

0

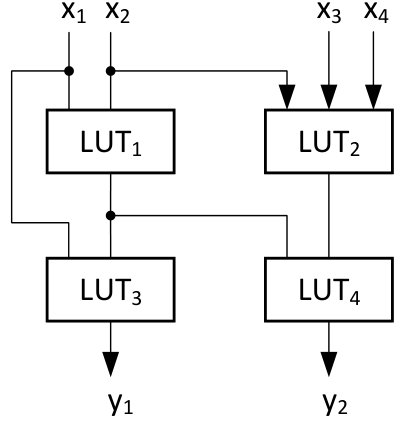

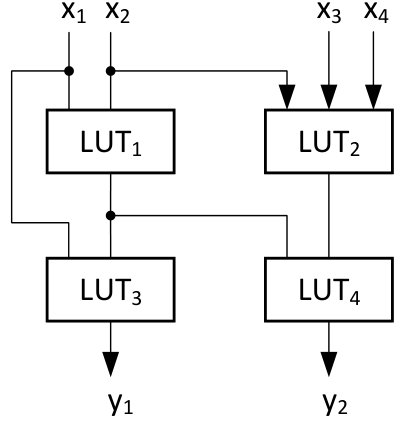

Анонс книги Параунитарные банки фильтров в алгебре кватернионов для систем кодирования изображений в ограничениях арифметики с фиксированной

Продолжаем публиковать книжные новинки и выбивать небольшие, но все же скидки на них.

3234

0

Краткая сводка научных статей, с упоминанием FPGA/ПЛИС (Март 2024 / часть 1)

Предлагаем читателям небьольшую подборку зарубежных начно-технических статей с упоминанием ПЛИС

- Реализация гибридного метода маркировки пятен волнового фрон

...

Читать дальше »

3652

0

FPGA 2024.1 : Слёт и второй номер журнала

ПЛИС-культ привет, FPGA комьюнити!

Два коротких объявления:

1. Ищем докладчиков для нашего слета FPGA разработчиков, который состоится в Москве-Питере-Новосибирсике/Томске в концеМая--началеИюня. Регистрация пока не открыта, но мы хотим сформировать программу заранее Т ... Читать дальше »

4603

0

Ускорение разработки на SoC и FPGA с помощью Vitis™ Model Composer и Vivado™ Design Suite

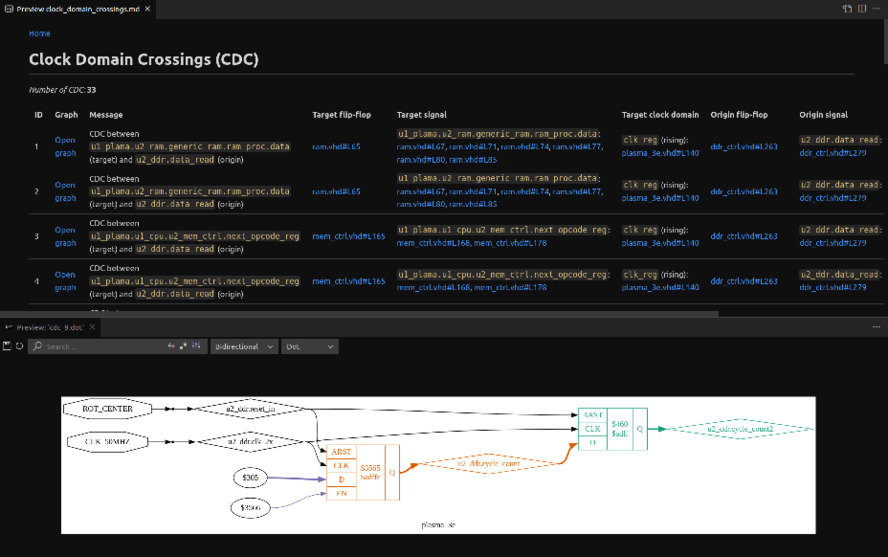

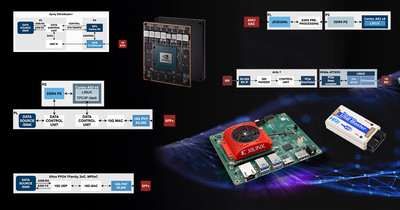

Vitis ™ Model Composer предоставляет собой среду для разработки алгоритмов и среду проектирования на основе моделей. Vitis Model Composer также предлагает различные методы для ускорения процесса разработки и упрощения интеграции сложных IP-ядер в проекты.

На этом вебинаре мы рассмотрим: ... Читать дальше »

7123

0

ПРЕДКОНФЕРЕНЦИИ РОССИЙСКОГО ФОРУМА МИКРОЭЛЕКТРОНИКА 2023

9-я научная конференция «ЭКБ и микроэлектронные модули», фундаментальное мероприятие российского форума «Микроэлектроника 2023», включает две предконференции, которые пройдут в сентябре 2023 года.

6864

0

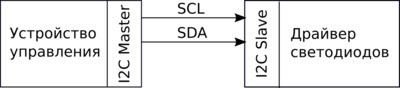

GOWIN Semiconductor приглашает на вебинар по i3c .

GOWIN Semiconductor приглашает на вебинар по i3c .

Компания GOWIN Semiconductor рада представить клиентам FPGA семейство продуктов I3C IP. На протяжении десятилетий I2C был широко используемым интерфейсом в электронной промышленности для настройки, сенсорного интерфейса и других приложений с низкой про ... Читать дальше »

6784

0

0