Статьи участников нашего сообщества

Модуль: Каталог статей

Обзор отладок с FPGA :: SP701

Продолжаем обзоры отладочных плат. Сегодня у нас SP701 - новейшая разработка от XIlinx, которой буквально пара месяцев от роду. Плата на Spartan-7 наиболее бюджетом кристалле семейства Xilinx. Несмотря на это у кристалла 400 пользовательских портов ввода / вывода. На плате 2 Ethernet, HDMI, FMC и 6 PMOD! Есть где развернуться.

О плате:

http://fpga-systems.ru/news/spartan_7_sp701_fpga_evaluation_kit/2019-07-12-79

Плата предоставлена КТЦ "Инлайн Груп" дистрибьютор и тренинг центр XIlinx в РФ http://www.plis.ru и http://www.plis2.ru

Группа в VK: https://vk.com/club185679360

Группа в Facebook:

https://www.facebook.com/groups/fpgasystems.ru/

Обсуждайте в чате Telegram @Powered_by_KeisN13

https://t.me/Powered_by_KeisN13

3773

Xilinx ZCU104 - еще один MPSoC кит доступен для РФ

Все же терпение дает о себе знать. Наконец то Xilinx расширил линейку своих отладочных плат с Zynq US+ MPSoC официально доступных для рынка РФ.

Напомним, что в виду наличия аппаратного шифрования внутри кристаллов семейства XIlinx Zynq MPSoC существуют ограничения на ввоз данной продукции со стороны РФ. Поэтому Xilinx специально выпускает серию MPSoC, в которых данный аппаратный блок деактивирован и данные кристаллы и платы на их основе разрешены для ввоза в РФ.

Сейчас доступны две отладки для РФ - это ZCU102 и ZCU106, в префиксе которых указаны две буквы ED - Encryption Disabled. Ну а теперь и третья отладка ZCU104, которую мы с Вами и рассмотрим более подробно.

4212

0

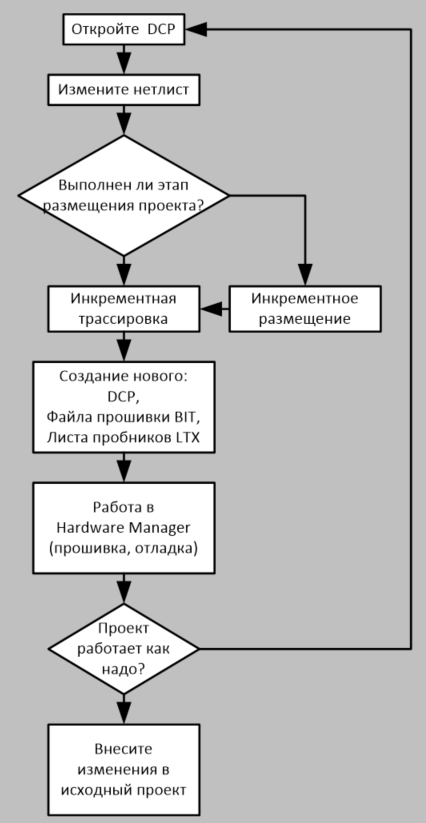

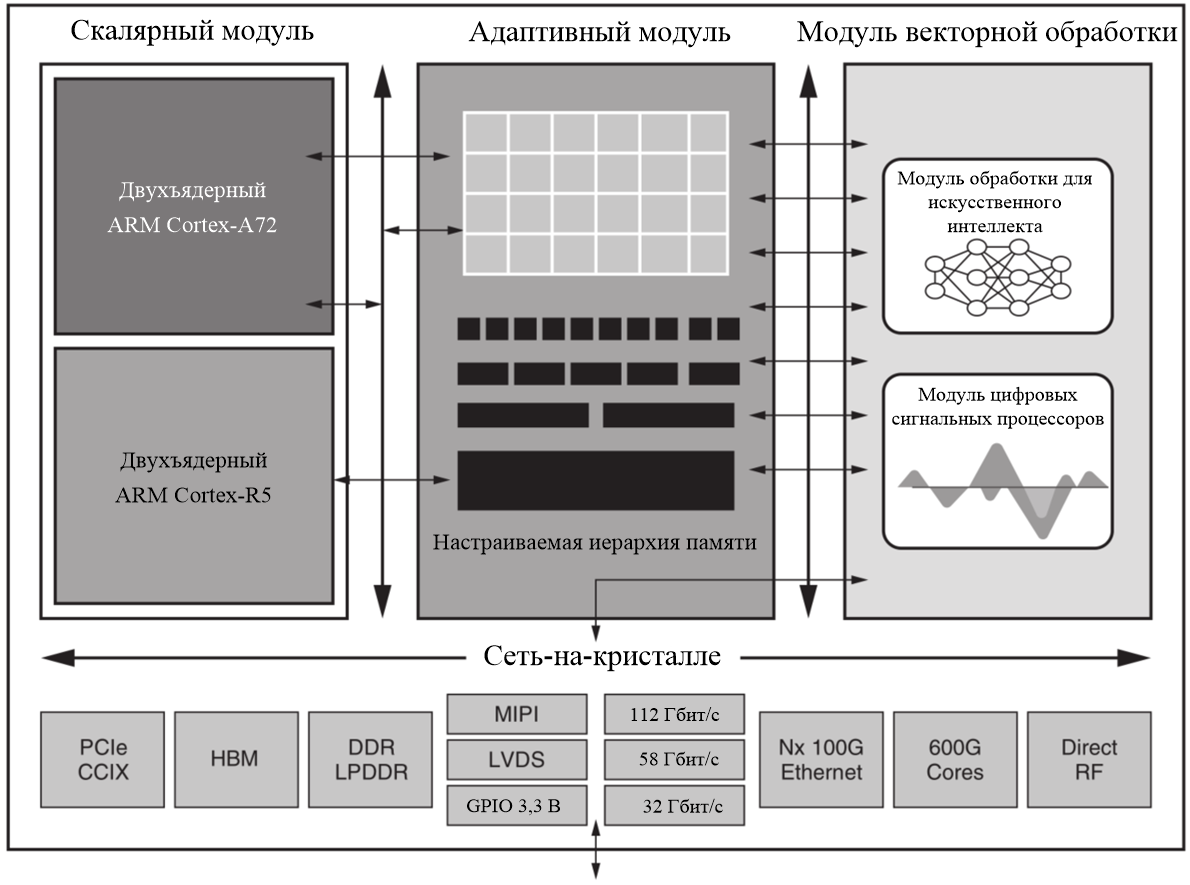

ECO Flow в Vivado или работа в режиме редактирования нетлиста. Часть 2

Продолжение руководства по работе Vivado Eco Flow

6199

0

ECO Flow в Vivado или работа в режиме редактирования нетлиста. Часть 1.

В статье рассмотрен режим работы Vivado, позволяющий вносить изменения в проект на уровне редактирования списка соединений (в дальнейшем – нетлиста). Описаны как сам режим ECO, так и некоторые нюансы, которые появляются во время работы в нём. Приведён демонстрационный пример и описана полная последовательность действий для получения результата, в работоспособности которой может убедиться каждый желающий. Статья будет полезна для «общего развития» FPGA-разработчикам, а особенно — тем, кто часто отлаживает проекты в Logic Analyzer. Надеюсь, работа в этом режиме вызовет интерес у разработчиков, работающих с большими кристаллами, время компиляции в которых может достигать часов (а то и десятков часов), поскольку в этом режиме время, затрачиваемое на имплементацию, при внесении изменений в нетлист может сократиться до буквально пары минут.

5067

0

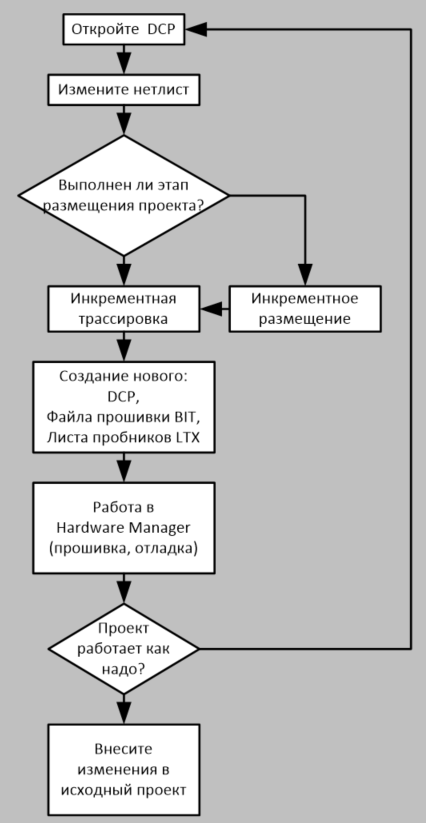

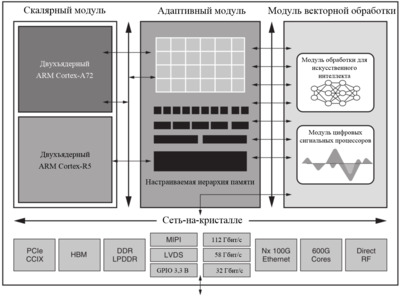

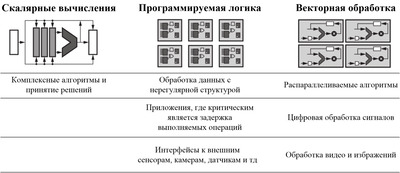

Xilinx VERSAL: монстр с NoC'ом

7417

0

Разработка IP-блока с помощью инструментов высокоуровнего синтеза: HLS Часть 3

В этой части будут показаны основные шаги необходимые для запуска и работы разработанной в прошлых частях системы [1, 2]. Будет показано, как можно использовать API, которое автоматически генерируется для IP-блоков с интерфейсом AXI4-Lite.

4813

0

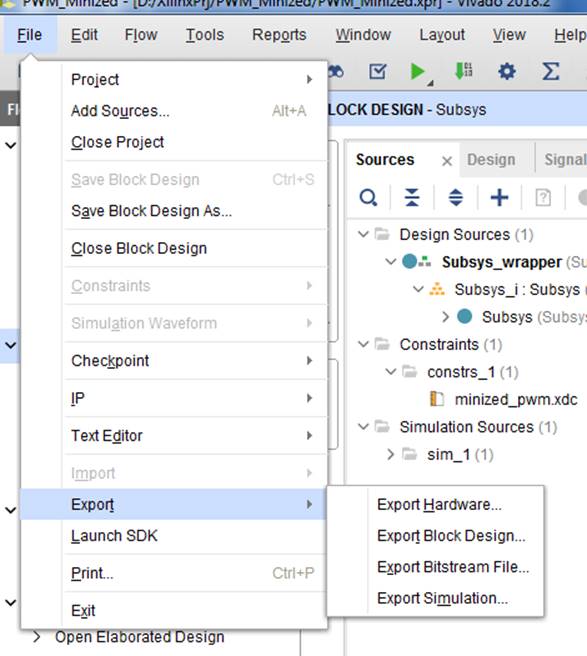

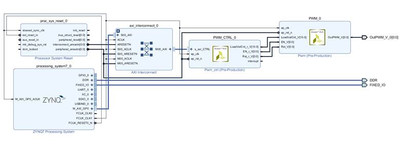

Разработка IP-блока с помощью инструментов высокоуровнего синтеза: HLS Часть 2

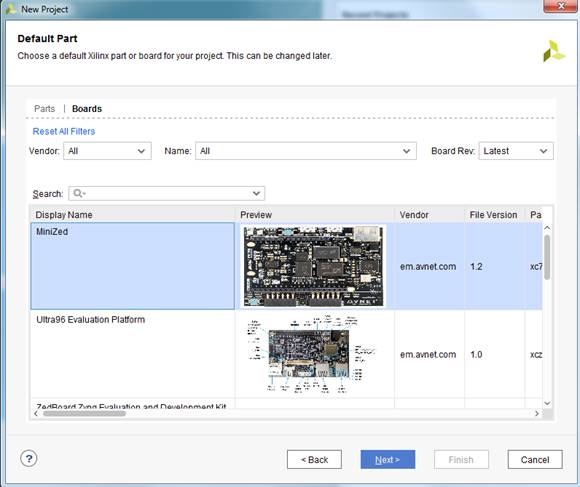

В этой части будут описаны основные шаги для создания блок дизайна (работа в IP Integrator) для разработанных ранее IP-блоков в среде Vivado HLS [1]. Интеграция будет производится для системы-на-кристалле ZYNQ-7000, а конкретно для Zynq установленного на плате MiniZed [2, 3].

7626

0

0