Статьи из раздела: Xilinx

Раздел: Xilinx

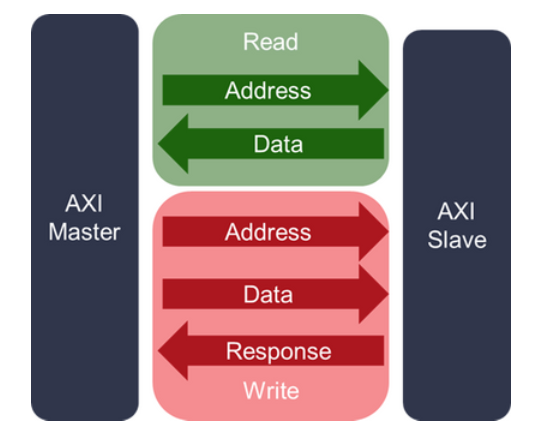

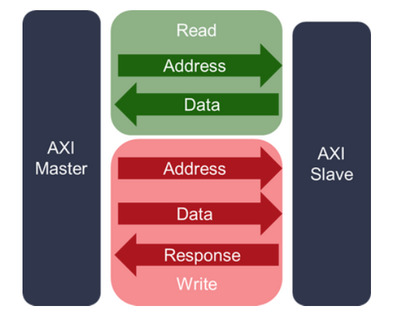

Основы AXI часть 6 – Введение в AXI4-Lite в Vitis HLS (часть 1)

В этом уроке мы будем изучать основы того как создавать пользовательские IP блоки с AXI4-Lite интерфейсом в Vitis HLS.

14252

Сможет ли HLS код побить HDL по производительности?

В этой статье мы задействовали инструменты Silexica SLX для FPGA, чтобы оптимизировать промышленное приложение для обнаружения и отслеживания объектов.

В этой статье мы задействовали инструменты Silexica SLX для FPGA, чтобы оптимизировать промышленное приложение для обнаружения и отслеживания объектов.

5220

0

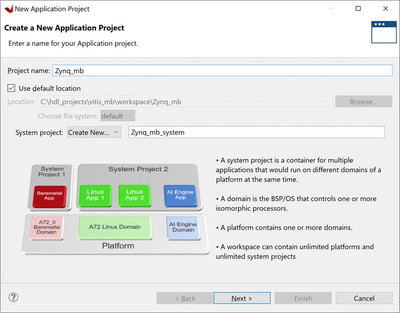

Создание многопроцессорной системы в Vitis: Zynq + MicroBlaze

Ранее мы рассматривали то, как мы можем использовать Vitis для встроенных систем на Zynq и Zynq MPSoC.

Другим важным аспектом Vitis является возможность создать платформенное решение, которое включает в себя различные элементы обработки в PS и даже в PL.

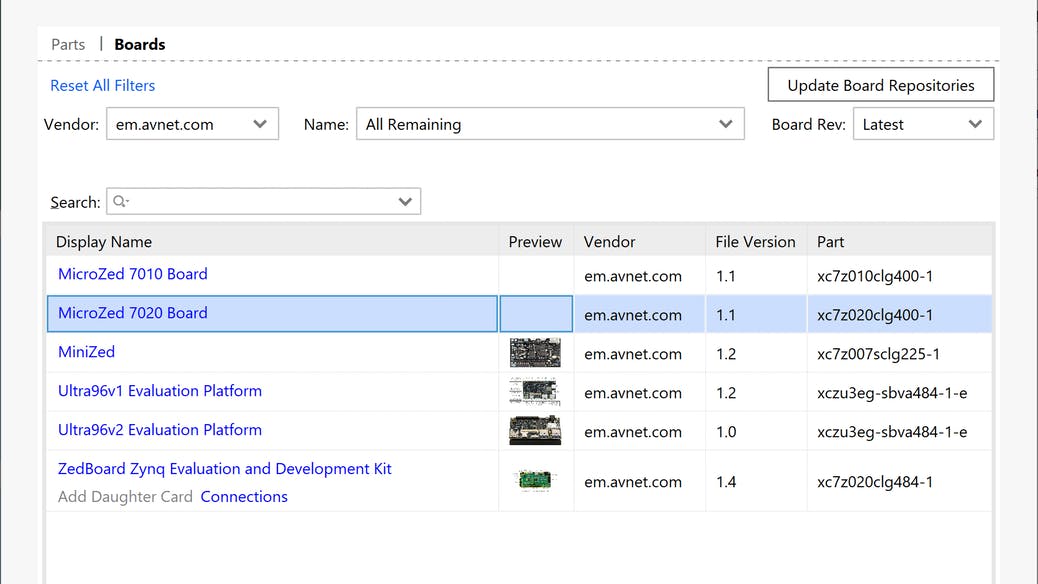

Сегодня мы рассмотрим, как мы можем использовать Vitis для разработки платформенного решения на Zynq, которое использует и Cortex A9 в PS, и MicroBlaze в PL. Нашей целевой платой будет MicroZed 7020.

Создание нового проекта

Первое, что нам нужно сделать, это создать новый проект, ориентированный на MicroZed 7020. После создания проекта следующим шагом будет создание блок-схемы и добавление в неё Zynq PS.

9188

1

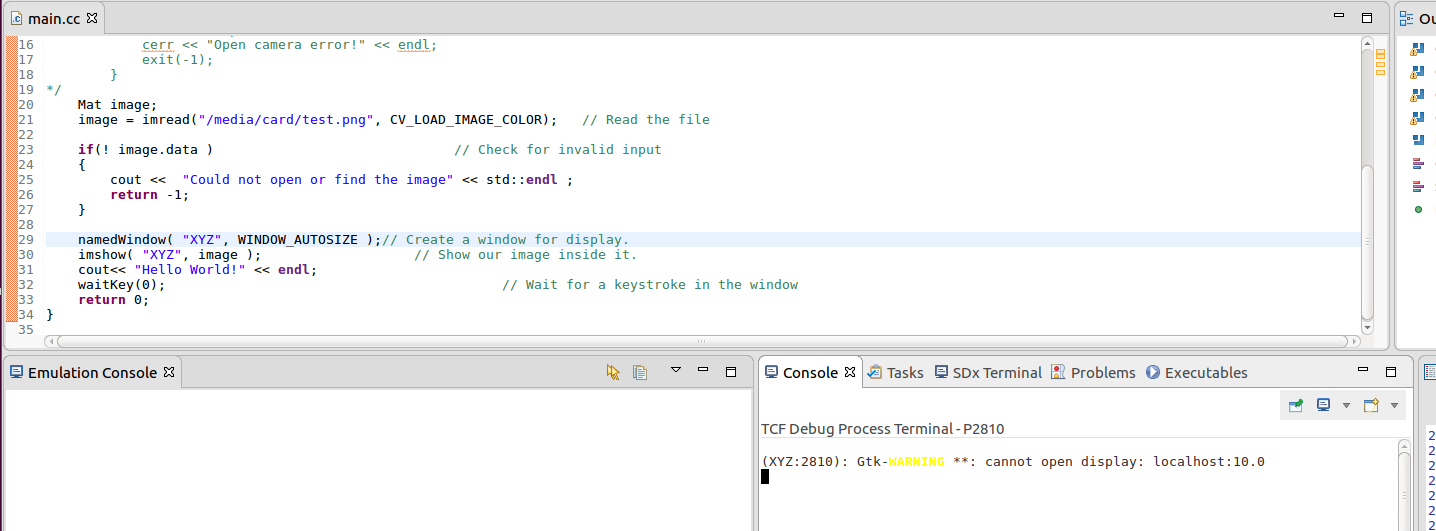

Визуальная отладка OpenCV приложений для Zynq US+ в Xilinx SDK

В данной статье рассмотрен один из способов вывода на экран изображения в SDK для отладки OpenCV приложения

4017

0

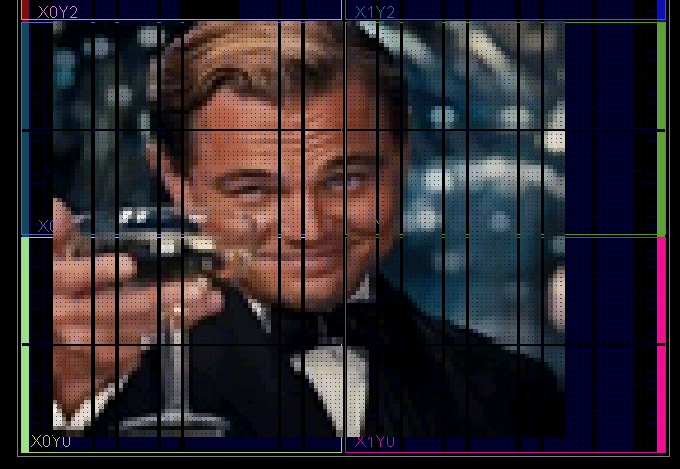

Vivado: Picasso mode

Безумию все возрасты покорны

При проектировании каких-либо модулей на ПЛИС невольно иногда приходит в голову мысль о не совсем стандартном использовании самой среды проектирования и инструментов, которые она предоставляет для проектирования. В этой небольшой заметке мы рассмотрим, как с помощью инструмента управления средой, реализованного на Tcl, мы можем буквально рисовать на ПЛИС фотографии, картины, портреты и мемасики.Такой необычный «маршрут проектирования» был реализован еще полтора года тому назад, но вот только сейчас пришла мысль оформить его в виде заметки, в которой имеется небольшая практика применения Tcl скриптов для управления средой проектирования, в данном случае Vivado. Однако при небольших доработках все легко может быть адаптировано под другие среды разработки, например Qaurtus II.

Вам доступна статья в формате PDF

6128

3

SP701 + PCAM-5C + 15 Минут+ VITIS = Easy MIPI на FPGA

Аннотация

5392

0

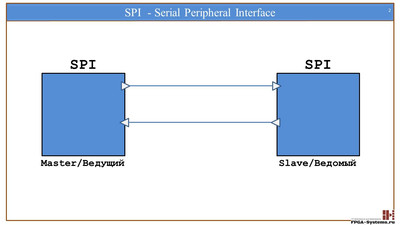

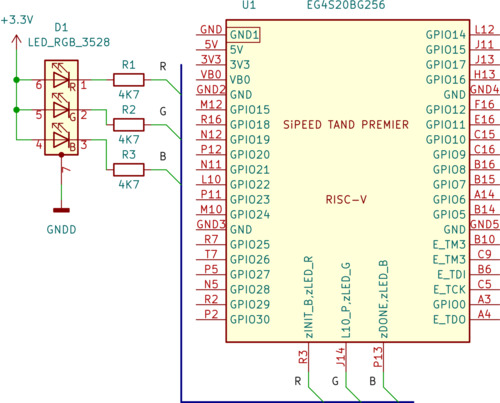

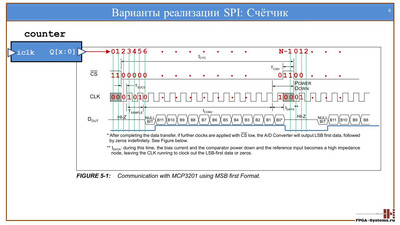

Интерфейсы :: SPI :: Часть 2:: Варианты реализации

Продолжаем работу над проектом по развёртыванию интерфейса SPI на ПЛИС. Сегодня мы с Вами обсудим варианты реализации интерфейса.

12871

0

0