Статьи из раздела: Xilinx

Раздел: Xilinx

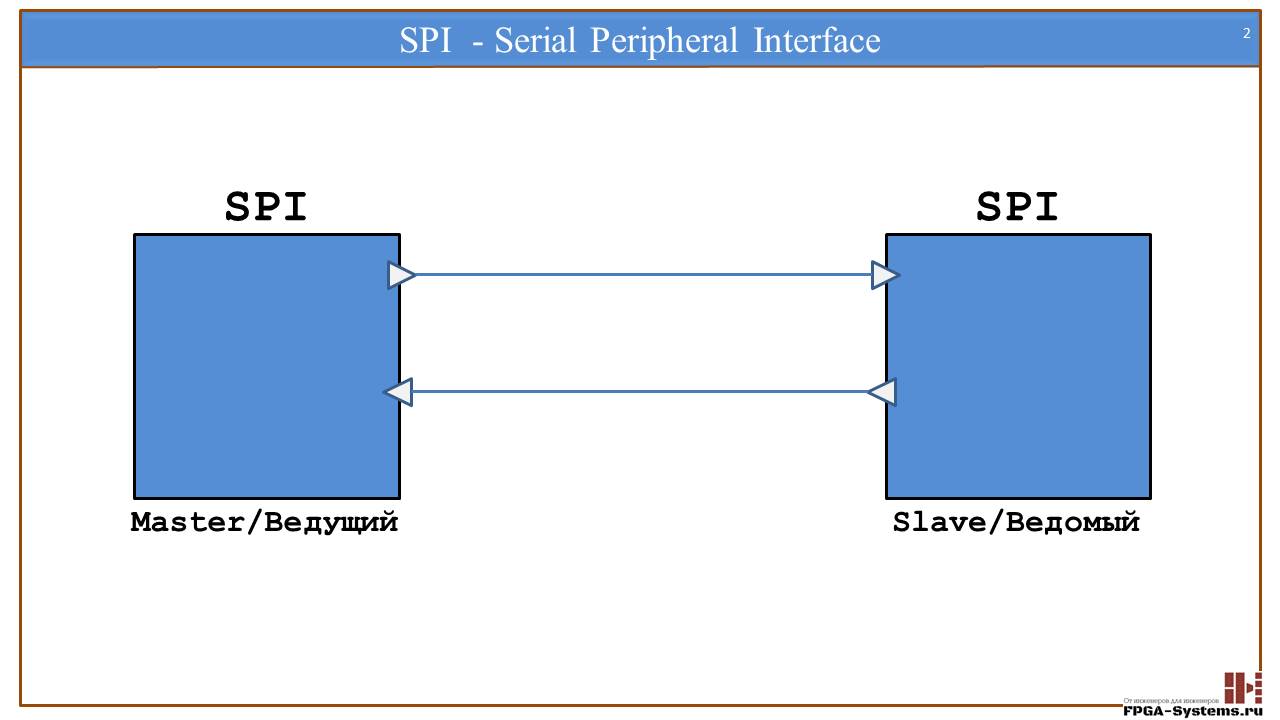

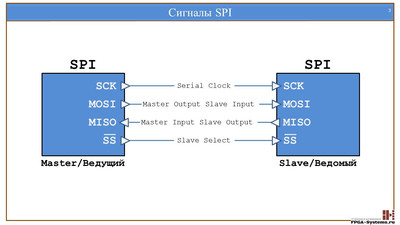

SPI :: Часть 1:: Общие сведения

Здравствуйте друзья. C вами проект FPGA-systems.ru.

Один из подписчиков попросил нас рассказать о разработке интерфейса SPI на ПЛИС. Ну что ж, не оставим его просьбу без ответа.

11368

ECO Flow в Vivado или работа в режиме редактирования нетлиста. Часть 2

Продолжение руководства по работе Vivado Eco Flow

8117

0

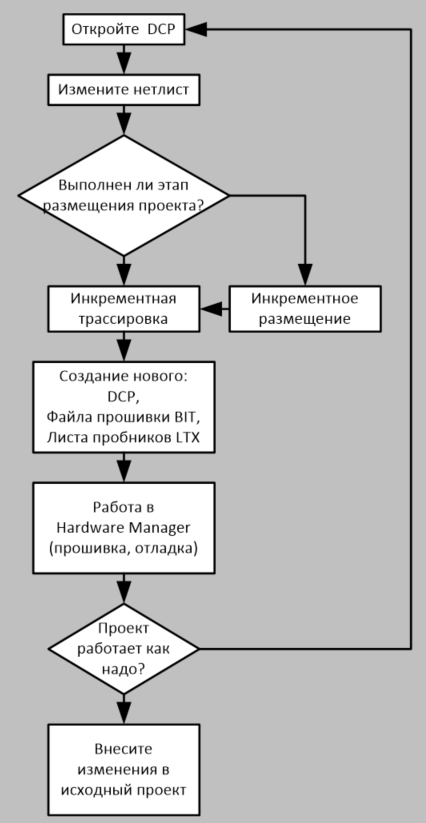

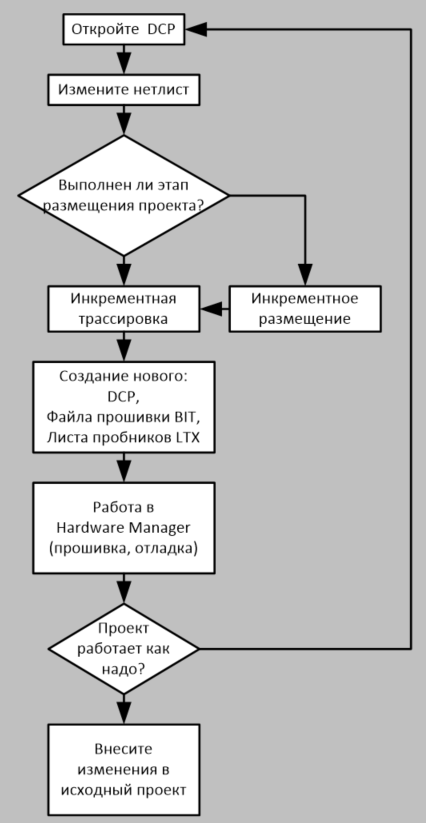

ECO Flow в Vivado или работа в режиме редактирования нетлиста. Часть 1.

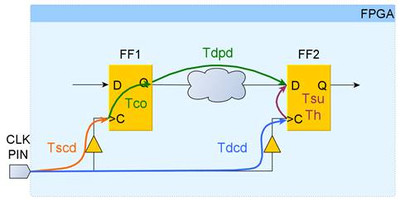

В статье рассмотрен режим работы Vivado, позволяющий вносить изменения в проект на уровне редактирования списка соединений (в дальнейшем – нетлиста). Описаны как сам режим ECO, так и некоторые нюансы, которые появляются во время работы в нём. Приведён демонстрационный пример и описана полная последовательность действий для получения результата, в работоспособности которой может убедиться каждый желающий. Статья будет полезна для «общего развития» FPGA-разработчикам, а особенно — тем, кто часто отлаживает проекты в Logic Analyzer. Надеюсь, работа в этом режиме вызовет интерес у разработчиков, работающих с большими кристаллами, время компиляции в которых может достигать часов (а то и десятков часов), поскольку в этом режиме время, затрачиваемое на имплементацию, при внесении изменений в нетлист может сократиться до буквально пары минут.

6482

0

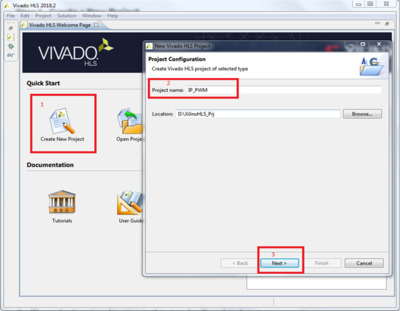

Разработка IP-блока с помощью инструментов высокоуровнего синтеза: HLS Часть 3

В этой части будут показаны основные шаги необходимые для запуска и работы разработанной в прошлых частях системы [1, 2]. Будет показано, как можно использовать API, которое автоматически генерируется для IP-блоков с интерфейсом AXI4-Lite.

5788

0

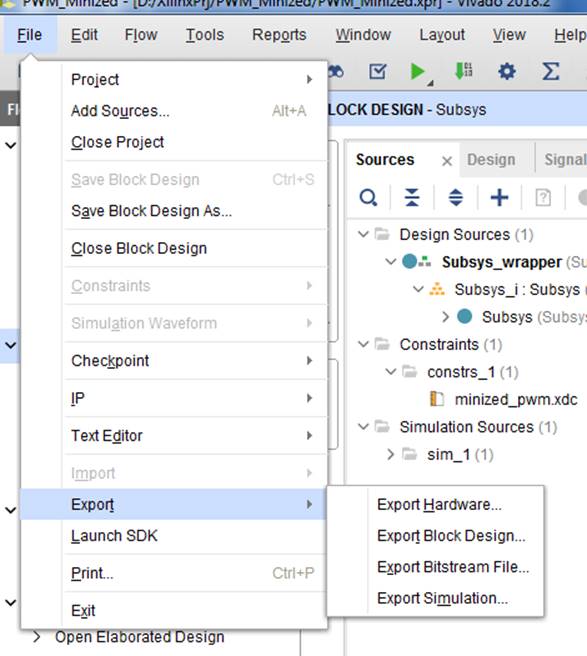

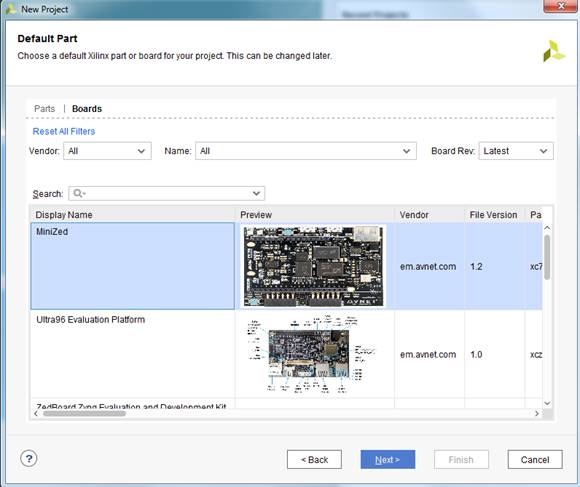

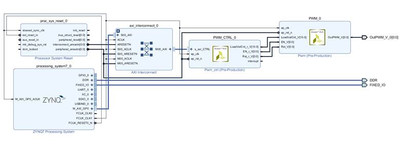

Разработка IP-блока с помощью инструментов высокоуровнего синтеза: HLS Часть 2

В этой части будут описаны основные шаги для создания блок дизайна (работа в IP Integrator) для разработанных ранее IP-блоков в среде Vivado HLS [1]. Интеграция будет производится для системы-на-кристалле ZYNQ-7000, а конкретно для Zynq установленного на плате MiniZed [2, 3].

9080

0

Minized: ZynqHW : 07 : Лабораторная работа №3

Проходим туториалы по Zynq-7000. Третья лабораторная работа, в которой мы активируем дополнительные аппаратные контроллеры, имеющиеся в процессорной системе и проводим их беглое тестирование.

Важно: в виду определённых политических причин доступ к данному контенту может быть предоставлен только зарегистрированным пользователям. Пожалуйста войдите под своим аккаунтом или пройдите регистрацию. Это займет 10 секунд.

Дополнительная информация:

Запрос платы: fpga-systems@yandex.ru (раздаем бесплатно)

Minized - http://zedboard.org/product/minized

5334

1

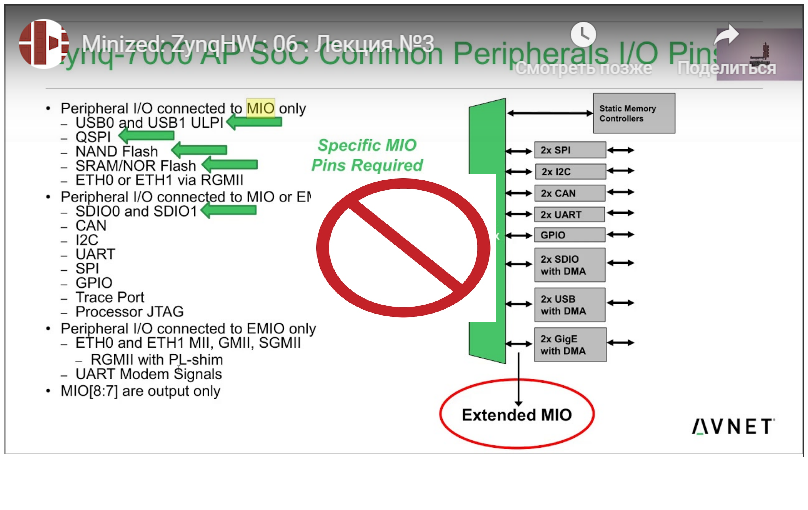

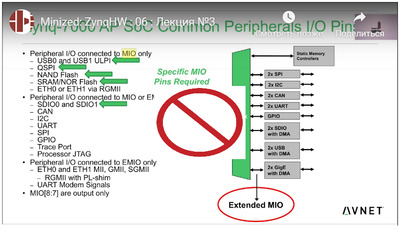

Minized: ZynqHW : 06 : Лекция №3

Проходим туториалы по Zynq-7000. Третья лекция посвящена краткому обзору встроенной периферии Zynq-7000 и ее особенностям.

Важно: в виду определённых политических причин доступ к данному контенту может быть предоставлен только зарегистрированным пользователям. Пожалуйста войдите под своим аккаунтом или пройдите регистрацию. Это займет 10 секунд.

Дополнительная информация:

Запрос платы: fpga-systems@yandex.ru (раздаем бесплатно)

Minized - http://zedboard.org/product/minized

2951

0

0